## Preface

The standardised hardware description language VHDL has become a widely used language in the electronic design community [24]. It is appropriate to describe hardware at various levels of abstraction that occur in a design flow. The language has proven to be appropriate from switch level modelling to behavioural descriptions.

This thesis considers it useful to enlarge the range of abstraction provided by the language and extends the language to raise its level of abstraction towards system level. Increasing the level of abstraction is regarded as an answer to the question how to improve modelling capabilities and efficiency of the language for large scale designs. The extension adds object-oriented features to VHDL. The extended language has a class-concept that is based on an extension to the existing type concept of VHDL [87], and an inheritance mechanism. Further it supports polymorphism. The extended language becomes a full object-oriented language. The extension comes with a translation concept allowing to integrate object-oriented hardware models in a standard design flow. An important feature of the translation concept is to preserve properties of a hardware description that are intended for a VHDLbased synthesis [125].

The presentation is based on the extension to VHDL, nevertheless, it provides an insight into object-oriented hardware modelling independently from the language extension that is of more fundamental nature. A contribution is to show close similarities between concurrent object-oriented programming, programming of distributed systems, and object-oriented hardware modelling. An analysis of existing languages for system level specification exemplifies the similarities. Among the similarities we focus on the modelling of communication and synchronisation between objects which we believe plays the important role in the design of abstract and re-usable systems. In that context we describe the conflicting between synchronisation constraints and inheritance that is known in concurrent object-oriented programming as inheritance anomaly [111]. A key contribution of this thesis is to provide a solution to the anomaly. Although the solution is formulated for object-oriented hardware modelling using the language extension to VHDL the principle behind it is of a more general nature and can be transferred back to concurrent object-oriented programming [156], where the anomaly originally was detected. In contrast to other approaches to extend VHDL, we do not only provide a re-use concept for data structure and behaviour but we also consider the re-use of synchronisation code which is an essential in the modelling of concurrent systems.

The structuring of the thesis intends a presentation that provides all the relevant information that is necessary to understand the basic problems of object-oriented hardware modelling and to follow the proposed solutions. Especially, the reader is not expected to have any special previous knowledge about concurrent object-oriented programming or object-oriented programming of distributed systems. After briefly presenting the context of hardware modelling we introduce object-oriented design principles. We provide the material from concurrent object-oriented programming and object-oriented programming of distributed systems that turns out to have similarities with object-oriented hardware modelling. As there is no agreement on a common terminology in the object-oriented design community, we give a short definition of the terms we introduce. A glossary of terms can be found in the appendix. Significant parts of the motivation to propose an object-oriented extension to VHDL can be found in an analysis of system level specification methodologies and in the discussion of other approaches to extend VHDL. A very short description of the basic features of VHDL may be skipped by those already familiar with the language.

The language extension to VHDL is introduced with many examples that should allow to understand its main ideas even without a detailed reading of all the previously presented material. The material presented in a discussion on the applicability of the language extension following the introduction of the language and in a discussion about the results of a corresponding case study may be viewed as a large example. The solution of the inheritance anomaly can be considered as an answer to the modelling problems that occurred in that example.

#### Acknowledgement

The ideas presented in this thesis are the results of my research at Carl von Ossietzky Universität Oldenburg.

I am indebted to my supervisor Professor Dr.-Ing. Wolfgang Nebel for making this research possible. I am grateful for his support and encouragement and I appreciate the freedom that he offered me while pursuing my research.

I would like to express my gratitude to Professor Dr. Dieter Monjau for his interest in this dissertation.

Thanks are due to my colleagues at the VLSI group for providing me with a creative environment and for stimulating discussions, particularly Wolfram Putzke and Martin Radetzki.

I must also take the opportunity to thank Martin Wilmes, Uwe Quiet, Bernd Tangemann, Tiemo Fandrey, and Sven-Olaf Scholz for supporting this thesis by elaboration of a case study and working on a prototype of a translation tool.

## **Chapter 1**

## Introduction

Object-oriented specification and design denotes methodologies that are successfully applied in software engineering to build complex software systems [28,44,142,158]. The object-oriented structuring and encapsulation of programs prevents the scattering of related information all over the system. The resulting software becomes robust, reliable, re-usable, and extendable. These are essential qualities for developing large and complex software systems at reasonable cost [128].

The electronic design community is looking for design automation that provides the same characteristics. It needs techniques to improve productivity and to manage large designs. It is a major concern that the reliability of the systems must not suffer from the increasing productivity and that large designs still are controllable in terms of testability and manageability [43].

A promising approach is to use methodologies that promote re-use of tested designs at all levels of abstraction. At system level this includes maintenance during the life-cycle of a product as well as re-use of systems as tomorrow's subsystems. A form of re-use that becomes more and more important for modelling is to use design components that are purchased as intellectual property. The requirements for designing systems-on-silicon are methodologies that allow technology independent re-use at system level [56].

Like programming, hardware design is about abstraction and decomposition of the design problem. The development of hardware design techniques has been concerned with the introduction of various levels of abstraction [109,140]. Today, the conventional abstraction technique for designing at system level is to use a procedural hardware description language [52]. In the software domain the procedural approach turned out to be inadequate for programming in the large. Enhanced encapsulation and abstraction mechanisms as they are provided by the object-oriented concepts were identified to be necessary for successfully handle large software systems [29]. The objectoriented paradigm as an approach to solve complexity and productivity problems in software engineering motivates the idea to apply it to hardware design.

We believe that only a change of design paradigms for modelling at system level can achieve the required improvements of design productivity. The intended development is to transfer the enhanced encapsulation and abstraction concepts of object-oriented modelling and its benefits to hardware modelling.

It is a goal of the thesis to illustrate how such a change of paradigms can gain the necessary improvements. We show that adding object-oriented features to the hardware description language VHDL performs the desired change of paradigms. We propose a small extension that can be integrated in existing VHDL-based design flows. Different to other proposals to extend VHDL, the approach in the thesis combines the language extension to VHDL with a new modelling methodology. The basic principle of the methodology is to carefully take the interaction between object-oriented modelling and parallel hardware designs into account. The new concept for modelling the interaction is viewed as a keystone for successfully developing robust, reusable, and expandable hardware designs.

The next chapter covers in outline the main goals of modelling in hardware design. It contains a discussion on the importance of hierarchy and abstraction in the design of robust and re-usable hardware models. The chapter brings out the deficiencies of procedural hardware description languages for system level modelling. It explains the modelling challenges for such systems and the resulting necessity for a change of design paradigms.

Object-orientation is proposed as the new design paradigm for modelling hardware at system level. The principles of object-orientation are provided in Chapter 3. The chapter discusses the usefulness of various object-oriented concepts for the re-use of models. Concepts for modelling parallel and distributed systems and their integration into object-oriented concepts are then introduced. The integration is identified as a key issue in object-oriented hardware modelling.

Chapter 4 analyses the potential of system level specification languages for use in hardware design. Similarly Chapter 5 presents an analysis of hardware description languages and their potential for system level specification. Particularly, the chapter provides a rather complete overview about objectoriented extensions to the hardware description language VHDL. The deficiencies of the presented languages are discussed. In essence, the deficiencies concern the integration of concurrency concepts into object-oriented concepts.

The following three chapters are the core of the thesis. Broadly speaking, they provide a solution to the integration of concepts for concurrency, distribution, and object-orientation in hardware design. The solution is based on an object-oriented language extension to VHDL and a corresponding model-ling methodology.

Chapter 6 introduces the language extension. The facilities for object-oriented modelling of parallel hardware systems are presented. This covers a translation concept from the language extension to standard VHDL that allows to integrate the language extension in a VHDL-based design flow. Chapter 7 rounds off the introduction of the language extension by an example. The example illustrates the major themes of modelling concurrency and of object-oriented modelling.

Chapter 8 provides a detailed discussion on these themes. Finally, the chapter presents the solution to the integration of concepts for concurrency, distribution, and object-orientation in hardware design.

## Chapter 2

# Modelling

In hardware design a model is a representation of a system or a part of it. It allows a designer to form a picture of the system he or she has to deal with. A model has to serve several purposes during the design process. The modelling methodologies have to reflect these purposes. The chapter presents the main goals of modelling in hardware design. The focus is mainly put on the modelling of digital hardware systems. We derive some basic requirements which models must meet and we discuss the basic principles of modelling which are used to achieve these goals.

### 2.1 Modelling Goals

A general goal of a model is to collect information about a system and to structure the information in a way that it is accessible to people who are interested in the system and its development. Typically there are several persons involved in the design and development of a hardware system with different knowledge and skills. Their vocabularies often do not match and even if they use the same word it might have different meanings. In such a case a model can serve as a way to exchange information between the different persons involved in the system design if the model is described by a well defined formalism which is understood by all the involved persons [158].

A model can be used not only to exchange information about the system at a certain point of time in the design process but also during the whole design process and further on during the life-cycle of the system. The goal of such a model is to serve as a reference during the design process and a documentation of the system during its life-cycle [79].

A model is a representation of a system which is used to describe very different aspects of the system. A modelling technique to show a particular

aspect of the system is called *view*. Sometimes we also call the model which shows the particular aspect view. Typical views which are used in hardware design are timing models, behavioural models, delay models, structural models, value systems etc.

It is a quality of a model that it tries to avoid any inconsistencies in the information about the system. To describe what is thought as consistent in a special modelling context a consistency model is used. We could think of such a consistency model as a kind of meta-model. The meta-model deals with information in models and their relation to each other and thus should guarantee the consistency of the different views of a system. Very often such relations in a consistency model can be described as a set of conditions which must be fulfilled.

#### 2.1.1 Specification and implementation

Two kinds of information are normally distinguished in a model. The first one is the information given by the customer of the hardware system. We call this kind of information requirements. The other kind of information is the one added by the designers which we call implementation knowledge or implementation data. Depending on the kind of information a model contains it can be either classified as requirement model or as implementation model. Most of the modelling methodologies make this classification although they may use different terms. A widely used term for the requirements model is specification. Also the modelling of a requirement model is called specification.

Typical requirements in the design of hardware systems concern the functionality of the system, the performance, the area of the system on a chip, the power consumption. Other requirements may contain components which are to be used in the system or definitions of interfaces to other systems in the form of protocols, etc. It is obvious that models of the components, protocols, etc. are required to model these requirements.

The final goal of the modelling is to design a model which contains all the implementation data that is required to produce the system and which is consistent with the specification. A requirement model can be very often replaced by an implementation model during the modelling process. This leads to the notion of transformation. Designing is the transformation of a requirement model into an implementation.

The overall transformation consists of a sequence of iteratively performed transformations. We refer to such a transformation as a design step. In such a

sequence an implementation model of a transformation may become a requirement model of the next transformation. After each transformation the resulting model must be consistent with the original one. Again, the consistency can be modelled by a kind of meta-model. The conditions describing the meta-model together with the original model form new requirements.

Other meta-models which are used in hardware design describe the design steps that are required to develop an implementation from a specification. Such meta-models are called *patterns* [67]. A hardware design flow can be viewed as such a pattern.

#### 2.1.2 Exploration of design space

In each design step a designer can build various models which differ in the way the given requirements are met. The transformation techniques used in a design step normally do not automatically guarantee that all requirements are met. This has to be analysed in additional design steps. Due to the complexity it is normally not possible to perform an analysis in all the details. To select a model out of a set of alternative models with only limited information is one of the most problematic issues in design. To analyse various models and to collect as much information as possible about them is called the *exploration of the design space*.

It is a goal of the modelling to enable the exploration of the design space by providing information in a model which is relevant for analysing the requirements. If one model from the design space is chosen in a design step this design decision should be documented as part of the model in a way the decision is understandable. In other words, the design decision should be treated as a special kind of implementation information.

During the design process an initial specification normally undergoes some modifications. Very often it turns out during the modelling that there are some missing requirements which have to become part of the specification. To make the effort not worthless which has been spent so far in the modelling of the system a modelling methodology should support the introduction of the new requirements into the model without needing complex redesign steps of already developed models. The modelling goal is to get a robust model with respect to modifications.

#### 2.1.3 Re-use of models

Re-use of existing models and meta-models is the key idea to reduce the design effort and improve design quality[69]. For example, many hardware systems have requirements considering the same views, e.g., timing behaviour or power consumption. In such cases it makes sense to think about a model of time or of power which can be re-used in many systems. To enable such re-use the modelling methodology must allow to describe such models independently from a concrete target system. We call such a model *target independent*. The example shows that a modelling methodology must allow to generalize about the concrete target system to a whole class of target systems to enable re-use. The *generalization* concept is relevant in many variations for re-use.

There is a great variety of technologies which are used to produce the hardware systems and the technologies are rapidly evolving. Therefore another important concept for re-use of models is to generalize about the technology. A target independent model then represents the *intellectual property* which can be kept when re-targeting the system to another technology. In other words, a hardware modelling methodology should support the modelling of technology independent models for re-use.

There is a wide variety of different specification and modelling techniques in hardware design. Among these techniques hardware description languages (HDLs) are successfully used for many modelling issues in a design flow.

### 2.2 HDLs in a Design Flow

This section explains how hardware description languages are used in a design flow to model hardware systems. It describes how HDLs are used to meet the different modelling goals.

We denote a well defined language which was designed to document hardware systems, in particular systems consisting of integrated circuits, as hardware description language. Different to more general purpose modelling languages, HDLs have some built in models and meta-models which can be used in many hardware descriptions independently from a concrete system.

Such models are for example timing models, delay models, value models and corresponding conflict solution models, transition models, and models for functional primitives. The generalization about a class of models enables the re-use. The scope a language allows to generalize about with its built in models is just its intended application domain.

It has been mentioned that consistency models are used in hardware design to describe the consistency between various views of a system or between models of different design steps. Basically, there are two concepts supported by HDLs, a verification concept and a validation concept.

Following the verification concept means that the HDL has a formal semantics which allows to reason about system models. The consistency model is a kind of formula and the consistency check itself is a mathematical proof. The problem with such a concept is the in many cases limited model complexity it can handle compared with the validation concept.

Languages which support the validation concept have a *simulation semantics*. Simulation semantics implies that there is a mapping from models which are described by a HDL to an algorithm. Simulation means to execute the algorithm on some stimuli data. Such HDLs are very similar to programming languages except to the fact that they have the built in models for hardware design. One of the most important built in concepts which are provided by HDLs are timing models. They often include concurrency concepts to express parallelism in hardware systems. The consistency models consist of a set of rules describing how to map value models, delay models, and timing models of the different simulation models.

Some HDLs have a *synthesis semantics*. That means that the language contains a meta-model how to transform an existing model which is described by the HDL into a new model by adding information to the model. The consistency model is embedded in the meta-model describing the transformation. Typically, it is just a consistency model which describes a set of possible transformations for a given model. To select a concrete transformation out of many others is the exploration of the design space as mentioned in the previous section.

An interesting aspect of simulatable models is the possibility to communicate about the model by simply looking at the simulation results without studying the model in detail or even without knowing the HDL which was used to describe the model. Such a model can be a good communication interface to a customer [66].

Designers who directly access the models written in a HDL must be able to analyse and understand information of a model even if it is extensive and complex. A designer also must be able to easily add new information to the model and modify the existing model without completely re-analysing or rewriting it. The language must provide corresponding concepts to structure the information, modify it, and manage its complexity.

The next section presents the two main techniques to manage the design complexity.

## 2.3 Introducing Hierarchy and Abstraction

### into a Design

The information of a model is decomposed into manageable chunks to break down the complexity of the model. If we first look at specifications this means that a set of interrelated requirements is decomposed into single requirements. The design steps then deals with each single requirement separately. This may allow to design a model in a design step that is an optimal solution with respect to the single requirement, however, in most cases it is only a sub-optimal solution with respect to all requirements if it is a solution at all. There is often no efficient technique which allows to decide how to successfully decompose the model. The design decision how to decompose the system is then based on heuristics or simply the designers experience. Very often a costly search in the design space is required to find an appropriate solution which meets all given requirements.

#### 2.3.1 Hierarchy

If a decomposition technique is iteratively applied to a design then this establishes a hierarchy in the model. We can think of a model consisting of submodels which in turn consist of sub-models. This establishes a *has-partsrelation* between the (sub-)models [1]. We also call this relation *has-a relation*. Examples are functional decomposition or decomposition of tasks into parallel tasks. Top-down design flows establish the has-a-relation by applying the decomposition technique on the specifications. The same has-a-relation can be established by composition of models from existing (sub-) models<sup>1</sup> in a bottom-up design flow.

After the decomposition or composition the separate sub-models are interrelated to each other. In many design techniques this is the weak point to handle these relations properly. A typical problem is that a local modification in a sub-model causes inconsistencies with other sub-models due to their

<sup>1.</sup> We subsequently use the term model for both, models and sub-models.

interrelation. This requires a re-analysis and probably a re-design of other sub-models. The decomposition is not stable under local modification of models. An example is the decomposition of a system into a data path and a controller. Introducing new elements to the data path may require a re-analysis and re-design of the controller.

#### 2.3.2 Abstraction

An approach to solve the problem is to provide the information about a model which is required to understand the interrelations to other models and to omit the information which is not relevant for that aspect. We could think of the model with the reduced information as a special view. The view abstracts from the details of a model. We call both the omission of information in a model and the resulting view *abstraction*. An abstraction hides the details of a model. Conly abstractions are used to model the relations between models. *Encapsulation* is the relation between an abstraction and the corresponding model with the detailed information.

If an appropriate encapsulation is chosen a model can be re-used. Appropriate here means that the abstraction must contain all information which is required to use the model in various contexts.

Another concept of abstraction is to omit information which is not present at that stage in a design flow. More detailed information has to be added in further design steps. In this sense every model can be seen as an abstraction of the system it represents.

Abstraction along with hierarchy is the key to manage the design complexity. We now discuss examples where hierarchy and abstraction are used in a design flow and how they are supported by HDLs.

#### 2.3.3 Levels of abstraction

Different levels of abstraction are distinguished according to the concepts which are abstracted in the models. The levels correspond quite nicely to design steps in a hardware design flow. A design flow which differentiates six levels of abstraction is given in [140]. The levels are system level, algorithmic level, register transfer level, gate level, switch level, and electrical level. The latter is often also called circuit level.

#### 2.3.4 Bottom-up design

If we look at the levels from a bottom-up perspective we can see that there are concepts to aggregate the basic elements from the circuit and switch level. Encapsulation concepts allow to use the abstractions of the aggregates at the gate level. The concepts are successfully applied in cell libraries of ASIC vendors. A cell in the library abstracts implementation information and at the same time it abstracts behaviour. The models generalize about the timing model. As previously mentioned generalization allows a separation of views which is in this case a timing view and a functional view. A very good example how such a separation can be done at cell level is described in the VITAL standard [88].

The abstractions with the timing view and functional view separated allows their re-use independently from each other. This makes functional decomposition possible which uses the functional view of the gates as submodels. Starting from a functionally decomposed model timing issues can be considered. The timing model can be re-used in scheduling considerations for more complex models which are built as aggregation of gate level models because the timing abstraction is independent from the actual gates. The timing models for the gates only differ in the actual values. For the scheduling it is not relevant which behaviour i.e. which operation is performed by a gate. This abstraction concepts allows low modelling costs of functional and timing models at gate level and a very high re-use of the gate level models.

Attempts to apply these modelling and abstraction concepts to complex parameterized macros in general purpose ASIC libraries failed. Today, only memory cells and analog cells are modelled as macro cells. There are several reasons for that. A macro may have some complex internal state. In that case a simple functional abstraction does not work and it becomes difficult to generalize the timing behaviour so that it is independent from the functionality and can be re-used. Today's HDLs do not provide abstraction mechanisms which allow a designer to understand the behaviour and timing model of a complex macro cell from its abstraction. To re-use such a model either the implementation of the model has to be analysed which increases the cost of re-use or additional documentation about the model has to provide the missing information of the abstraction. The improper abstraction is also an obstacle for the designer to efficiently find the desired model for re-use. Another reason why the modelling of compex parameterized macros fails is the generalization mechanism provided by today's HDLs. The mechanism is based on generic parameters. It requires the designer of generic parameterizable

models to think of all possible future application scenarios of the model and to consider them in the model. Abstraction here may introduce quite an overhead into the model and make it more complex and less optimal for a particular application. The modelling effort is very high due to the very large number of possible combinations of actual parameters which have to be considered in a validation of the model. Large parameter lists are difficult to manage by a user. As a result there is only a limited re-use of parameterized macro cells while the modelling effort is high.

To summarize, we can say that there are limits in the useful modelling of complex macro cells due to missing abstraction and generalization concepts in the HDLs.

#### 2.3.5 Top-down design

To overcome the limits of bottom-up approaches abstraction mechanisms are applied in top-down design flows. In a top-down design step information can be added to a model through synthesis. This approach is used for place and route, technology mapping, and logic synthesis. It also can be used for higher levels of abstraction with register-transfer-level synthesis or behavioural synthesis.

In the top-down design flow the original model can be interpreted as an abstraction of the more detailed model which is at a lower level of abstraction. This approach can be used if there is tool support for the automatic synthesis of the abstract model. In that case it is possible to re-use the consistency model which is defined between the abstraction and the synthesis result. At the same time design knowledge is re-used. We can think of this knowledge as a meta-model which is encoded in the synthesis mechanism.

To enable re-use of both, the meta-model and corresponding synthesizable models it is necessary to provide a generalization concept about target technologies. This allows the modelling of technology independent models which can be re-targeted to a new technology by providing generic technology information to the synthesis tool in form of some technology libraries.

As described in the modelling goals, a synthesis mechanism should be robust. That means that a local modification in the abstract model causes only local modifications in the synthesis result at the lower level of abstraction.

#### 2.3.6 Register-transfer-level modelling

Today, technology independent design of synthesizable models is applied at register-transfer-level. In many cases the synthesis concept works quite well at that level[40]. The data model is some kind of re-usable bit-vector representation which normally does not introduce any instability in the synthesis mechanism. What causes problems are modifications of the abstraction which affect the functionality or the timing behaviour of the system. The timing behaviour may change locally due to local modifications of the functionality. However, the modification may cause a global effect in the synthesis mechanism. For example, introducing some components in a data path at register-transfer-level may require the re-analysis and design of the corresponding controller. We can identify two reasons for that. First, the state model is built separately from the functionality although they are interdependent i.e., the encapsulation concept at register-transfer-level is weak. The second reason is that modifications of the functionality may change the timing behaviour of the system. However, this modification of the timing behaviour is not reflected in the abstraction of the functionality. In other words, if we interpret the components in a register-transfer-model as limited resources we could say that there is no appropriate abstraction of the scheduling.

#### 2.3.7 Behavioural modelling

Behavioural modelling and synthesis which is used at algorithmic level provides an abstraction of scheduling. HDLs<sup>2</sup> for modelling at that level have some procedure-like concepts to abstract, encapsulate and decompose behaviour[110]. A procedure models an algorithm. It consists of an interface and an implementation. The interface only allows to pass information to the implementation via parameters and thus encapsulates the model in the procedure implementation. The idea is to look only at the interface to know what the procedure does and where it can be used. In other words, the interface abstracts from the implementation. Basically, the implementation consists of some kind of local variables and a sequence of statements. The variables can be used to model resources which are hidden outside the procedure. Causal relations which are implicitly given by the sequence of statements including some control statements abstract from timing relations concerning the com-

<sup>2.</sup> Although the focus here is on HDLs we can apply the following considerations to procedural languages in general.

mon access to a resource. The sequence of statements abstracts the scheduling.

Another important concept of modelling at algorithmic level is the possibility to hierarchically decompose procedures. This allows to functionally decompose an algorithm into manageable chunks. Each procedure which models such a chunk can be synthesized separately and then assembled to the complete algorithm.

The advantage of the procedural modelling is the possibility to keep modifications of behaviour in a model local. If an algorithm modelled by a procedure requires a modification it can be performed locally and it becomes effective globally at each place in the model where the abstraction of the modified procedure is used.

An example of an application domain is digital signal processing (DSP). A typical computation in DSP is a filter operation which operates on an input sequence to produce an output sequence. On each sample in a sequence the same sequence of operations is applied. Procedures are appropriate to encapsulate the sequence of operations. The procedure can be re-used for each sample. If modifications of the model are required then the encapsulation keeps modifications of the filter operation locally.

The sequence of operations in the procedure abstracts from the scheduling of the linear operations in the filter. The timing relations between the operations, i.e. unit delays, are modelled as causal relations.

The example shows the possibilities of procedural modelling and at the same time its limitations. It is not possible to encapsulate the internal state of the filter in a procedure because internal variables do not exist after the execution of the procedure. That means that state variables must be modelled as global variables. The disadvantage of global variables and thus the procedural modelling is that modifications of the data cannot be kept locally. The reason why procedural modelling can be nevertheless successfully used in DPS is that typical modifications of a model do not significantly concern the data. All the data is modelled by some numeric types. Modifications only concern some accuracy issues.

The example shows the modelling limitations namely the missing robustness with respect to modifications of data. The example also illustrates that procedural modelling is appropriate to encapsulate functionality and that it allows to abstract simple timing relations like unit delays.

#### 2.3.8 Modelling parallelism

If a model contains more complex timing relations a model consisting only of sequential statements often is not appropriate[66]. This requires a modelling methodology which is well-suited for modelling parallelism. A typical approach is to use a modelling concept which is considered orthogonal to the procedural modelling. Orthogonal means that a model which is decomposed into parallel tasks may contain any hierarchy of procedures. Timing relations between parallel tasks are described by synchronisation and communication models. HDLs which are designed to model at that level of abstraction provide a set of built-in models for communication and synchronisation.

The models abstract mechanisms to synchronize activities in parallel tasks and they abstract the exchange of information between tasks. There is a large number of very different models. On the one hand there are very powerful models like for example a rendezvous-concept and on the other hand there are mechanisms like low-level signals. The powerful models abstract very complex mechanisms. They may require mechanisms like for example routing strategies or queues which are costly to implement in hardware. In many cases such a complex mechanism introduces quite an overhead in the model where the synchronisation model is used. There is no direct mapping of such abstract models to lower level models. This is an obstacle in introducing a synthesis semantics to a language which has such complex built-in models.

For that reason today's HDLs tend to support only low-level synchronisation models. They allow a direct mapping to a hardware implementation. However, these low-level models do not meet the requirements for modelling at system level. The solution is that the hardware designer has to build complex communication and synchronisation models from low-level constructs.

The problem with procedural languages are the missing concepts to encapsulate and abstract user defined<sup>3</sup> synchronisation and communication models. Apart from the data which is transferred in a communication a synchronisation model contains quite complex control information but as mentioned above there is no possibility to encapsulate the control data.

There is also a more general problem of procedural modelling in the context of parallelism. If a synchronisation model is used in a procedure the procedure interface does not contain any abstract information about the model.

<sup>3.</sup> User defined means the synchronisation and communication is modelled by the hardware designer as opposed to built-in models.

However, the synchronisation model causes an activity outside the procedure namely the synchronisation with some other activities so that the model breaks the encapsulation. In other words, the procedure interface is not any longer an appropriate abstraction of a procedure. We have to conclude that procedural modelling is not orthogonal to modelling parallelism.

#### 2.3.9 Deficiencies of procedural HDLs

Another unsolved issue of today's HDLs is a missing re-use concept for synchronisation models. The idea is that an abstraction should support re-use by allowing to generalize about the data which is used for the communication and the activities which are performed during the synchronisation. The synchronisation model becomes a meta-model.

As a result we can say that today's procedural HDLs are not appropriate to model complex synchronisation. We also can conclude that a modelling methodology and a corresponding HDL should provide an abstraction and encapsulation concept for data and a generalization concept which allows to model re-usable meta-models.

The explanations and examples given in this chapter show that bottom-up and top-down concepts for hardware modelling with today's HDLs both have limitations which restrict their use at system level. The limitations mainly concern concepts for abstraction which allow to break down the complexity of models and which allow the re-use and modification of models. What has to be improved are concepts for generalization and abstraction at higher levels of abstraction.

#### 2.3.10 A new modelling methodology

The goal of the thesis is to develop a methodology for the modelling of robust and re-usable specifications at system level. The methodology is based on a HDL with simulation semantics to support validation of the specifications by simulation. It should be possible to add a synthesis semantics to the HDL which allows to integrate the methodology in a high-level design flow.

The approach in the thesis is to investigate the concept of parallel objectoriented modelling which is used in software engineering and to analyse its suitability for the hardware design at system level. Part of this work is to develop an object-oriented modelling methodology for hardware design and a corresponding HDL. The approach is motivated by the idea that object-oriented techniques provide concepts for generalization and abstraction which promise to solve some major modelling problems including the ones discussed above. Advantages as they are known from software domain include the design of robust, maintainable, and re-usable models. The re-use concept of object-oriented modelling allows the modification of re-used models. A proper encapsulation concept allows to break down the complexity of models and to reduce its maintenance costs.

While there are great benefits in using object-oriented methodologies, nevertheless we have to be aware that there are still some unsolved modelling problems. They have to be considered when adopting the methodology for hardware design.

#### 2.3.11 Modelling challenges

One of the problems that has turned out is that re-use of models is only possible under certain circumstances and only to a certain extent [105]. The idea to re-use models at system level as pluggable components in more complex models requires well defined interface concepts and a very complex communication structure<sup>4</sup>. An example for such an approach is CORBA (Common Object Request Broker Architecture). The high costs of designing the communication is an obstacle for generally using such a re-use concept for all kind of application. In fact it is mainly used for standard applications.

Another unsolved issue is the question what is the best way to integrate parallelism and object-oriented modelling. There have been a number of very different approaches. However, there is no final answer to that question yet. It is still a topic of research [115].

Although our modelling methodology aims at hardware design we try to address some of these issues in such a general way that the solutions can be used in the software domain too.

### 2.4 Overview

To introduce the terminology which is used in this book and to give a foundation to understand our modelling methodology the next chapter presents

<sup>4.</sup> It is interesting to note, that recently an initiative has been started with the Virtual Socket Interface Alliance to introduce such a concept of standardized communication mechanisms between models to hardware design.

object-based and object-oriented modelling concepts. It gives an introduction how to model parallel systems and it discusses the problems when integrating parallelism and object-oriented modelling. Chapter 4 is a survey on specification languages which allow to specify systems at a high level of abstraction. It analyses their potential for use in hardware specification. Chapter 5 is an overview of HDLs. Particularly, it explains the most important features of the hardware description language VHDL and covers the basic concepts of the language from a system level designer's point of view. It explains its main limitations with respect to system level modelling. The chapter also discusses existing language extensions to VHDL which try to overcome the limitations. It explains why there are still some unsolved issues. Chapter 6 presents our modelling methodology which is based on an object-oriented language extension to VHDL. Chapter 7 illustrates the methodology by an example. The example reveals some principle problems of object-oriented hardware modelling that concern communication and synchronisation modelling. Chapter 8 provides very detailed material on how to solve these problems. The concluding chapter provides the results of the earlier chapters in a very condensed form.

## Chapter 3

# **Principles of Object-Orientation**

In the previous chapter, we introduced the term object-oriented modelling and announced it as a key issue which shall be investigated in the context of hardware design in this thesis. However, we have so far not explained what the term object-oriented means. It turns out that although many methodologies claim to be object-oriented there is no common understanding of what object-oriented is. It is therefore impossible to give a precise and generally applicable definition of object-oriented modelling. In this chapter we explain what we think are the basic characteristics of object-oriented concepts. We describe the terminology as it is used in the context of the modelling methodology we are going to present in this thesis.

It seems best to start with object-based modelling philosophy on which object-oriented methodologies are based. We then dwell upon object-oriented concepts. We discuss the modelling of parallel systems and try to give an object-oriented view on process-based modelling and more general on object-based parallelism.

### 3.1 Object-Based Modelling

Object-based modelling concepts evolved from the idea to improve the abstraction of procedural modelling. A first improvement was achieved by putting related procedures together in a module. A module provides the procedures as services to a client. It consists of an interface and an implementation which separates the declaration of a procedure from its implementation<sup>1</sup>. The interface of a module contains the procedure declarations. It is an

<sup>1.</sup> In the context of procedures and modules we also call the implementation body.

abstraction of the services which a module provides. Only the abstraction is visible to clients the implementation is hidden. The limited visibility from the clients perspective is called *encapsulation boundary* [173] or *abstraction boundary* [172]. At the same time there is a boundary from the implementation's point of view concerning the visibility of entities from within the module implementation. It is the boundary of names, identifiers, references etc., that are visible when looking outward from within the module. This boundary is called *distribution boundary* [173]. Typically it includes the interfaces of those modules of which it is a client.

So far, the sketched module concept only provides services on transient data. After the execution of a service the module does not remember the effects of the execution. It has no memory.

#### 3.1.1 Objects

To overcome this limitation some module concepts allow to declare variables in a module body which are global with respect to the procedure implementations and thus accessible within the module body. We call such a variable *state variable*. Their values are called state. The data structures which implement the state variables and which store the object's state are referred to as *structure*. State variables are hidden from a client. The variables are the memory of the module and the only access to the memory is via the services provided by the module. State variables remember the effects of the execution of the services. The services form what is described as behaviour.

We call such a module which encapsulates structure and behaviour *object*. Structure and behaviour are *properties* of the object. Subprograms which implement the behaviour of an object are often called *method*, *operation*, or *primitive operation*. We could think in this context of a more general concept to implement the structure of an object. Such a more general concept may allow for example a structure to be implemented by other objects. A state variable turns into a container of an object. If we have this more general notion of a container we call such a container which is part of a structure *attribute*. If the object is inextricably linked to the container we call the object to implement its structure and the included object is the has-a relation or has-parts relation that was introduced in Section 2.3.1.

#### 3.1.2 Clientship

Modelling a system with objects means to describe objects and the relationship between them. The basic relationship between objects is the *clientship*. It describes how a client object uses the operations of a server object. An example of such a relation is the has-a relation. In the relation the server is encapsulated by its client. The server can be regarded as a private resource of the client [17]. We call such a server *sub-object* or if we want to emphasize the encapsulation we call it an *exclusive sub-object* of the client [57]. In another clientship an object is a server which might be shared by several clients. We call the clientship *use-relation*.

The interface of an object can be regarded as a contract between the object and its client [172]. The contract specifies both, the object's and the client's responsibilities and probably some general promises about the object. In a general sense, responsibilities of a client are called *preconditions* responsibilities of the object in responding are called *postconditions*. General promises about the object in form of a condition which always holds are called invariants. Preconditions, postconditions and invariants are assertions. A design approach which uses such assertions to describe a client server contract is called *design by contract* [159]. Assertions typically refer to information which is affected by the execution of an operation. This includes especially a state of the server. To take effect the contract must be visible to a client. As a consequence information about the structure of a server is made visible to the client. In other words, an assertion referring to the internal structure of a server circumvents in a way its encapsulation. It moves the abstraction boundary to include information about internal structure of an object<sup>2</sup>.

An important property of assertions is to introduce redundancy into a model. Assertions promise or specify properties of objects which have to be implemented by an object's implementation. Assertions as part of the specification describe what an operation does i.e., its behaviour. The implementation describes how to model the behaviour. To have a solid model it is necessary to check the consistency between these two aspects of the same

<sup>2.</sup> If information about an object's structure becomes visible outside the object it does not necessarily mean that the structure is directly accessible. This must not be confused. Later on, we shall point out this distinction where it is relevant. In the design by contract approach described above, encapsulation is not violated with respect to accessing the internal state of an object.

behaviour. This can be done statically by analysing the model and dynamically during the execution of the model.

The idea of statically analysing the consistency between assertions and implementation is used as a concept for verification. The assertions become *verification conditions* [20]<sup>3</sup>. Checking the consistency means to prove the conditions. In other words, it means to check if the implementation fulfils the specification. Instead of referring directly to the structure of an object the verification conditions refer to information which describes the internal structure and which is part of the interface. The information about the structure is duplicated in the interface and thus redundant information. Redundancy is used to achieve reliability. Although it would be desirable, there is no automatic proof mechanism. In most cases there is at the most tool support for the manual verification of the conditions. This is the reason why such an in theory interesting approach to abstract the behaviour<sup>4</sup> of an object in a specification is not more often used in practice.

Taking the contract point of view on an interface means that a contract is a special kind of abstraction on how to interact with a server. If a client wants to use a service of the object it has to send a *message* requesting the service to the object. This requires a message passing mechanism which allows to identify and address the server. A mechanism to identify objects is to give them distinctive names. These names become part of the object's interface, i.e. its abstraction and can be used to address them. For example, to address an exclusive sub-object it might be sufficient to simply use the object's name as an address.

A message has to be conform to the contract between client and server. The rule that governs the communication between them is called *protocol* and the contract is a part of it. The contract between the client and the server models the clientship.

<sup>3.</sup> The approach presented in [20] is based on abstract data types (ADTs) which define a set of objects with a set of operations that characterize the behaviour of those objects. The verification conditions are modelled as proof annotations which abstract the implementation of the operations.

<sup>4.</sup> We shall see later on, how this insight into concepts of abstractions which use conditions can be applied to considerations about the abstraction of concurrent objects and their synchronisation.

#### 3.1.3 State-oriented view

If we regard an object with its internal state as a state machine then we talk about causing an event when a client sends a message and an object may react to an event when it receives a message. In this state-oriented view an execution of an operation which may change the value of the object's attributes performs a state transition. The event which causes the transition is called trigger event. Modelling languages which support a state-oriented view may provide dedicated language constructs to model states and state transitions. In other words, they have a built-in meta-model of states. This separates two kinds of states in the modelling: States modelled by the built-in meta-model and states modelled by explicit attributes. State transitions are modelled by the built-in meta-model and by the assignment of values to the attributes. Such a modelling language splits up an operation by separating the built-in state transition from the rest of the operation. We call such a rest of an operation *action*. From a modelling perspective the separation leads to the notion that a message causes a state transition and the built-in state transition metamodel then causes the execution of the corresponding action.

An action may contain assignments of values to attributes and thus may change an object's state. An important difference in the modelling possibilities between built-in state transitions and actions is caused by different distribution boundaries. The distribution boundary of a built-in state transition is the object whereas an action may have a broader boundary. This allows to model side-effects in an action by sending message to other objects.

Another concept of built-in state models is the so-called *activity*. Similar to an action an activity can be viewed as a part of an operation. However, its execution is not caused by a state transition but by entering a state which is modelled by the built-in state model. We call an object which has one or more activities an *active object*. Objects which are not classified as active are called *passive objects*.

The distinction between action and activity becomes relevant if we model parallel systems. In a model of such a system state transitions of the built-in model and corresponding actions are not interruptible by trigger events causing new transitions. Such trigger events are either queued or ignored during the execution of an action. This is different to activities. If an object is in a certain state a trigger event may cause a state transition even if an activity is executed. Such an event is able to interrupt the activity.

In a parallel system a built-in meta-model of states can be used to model just those states which contain the information which is needed only for synchronisation purposes. The resulting state machine is an *implementation*<sup>5</sup> of the protocol that describes the synchronisation. We shall look at the modelling of active objects and protocols in the Section 3.3 in more detail.

Given such a state-oriented view of an object it is possible to transform it in an equivalent model without built-in state model which uses only explicit attributes to model state transitions. Equivalent here means that both models behave in the same way from a clients point of view. In a pure sequential model this transformation is quite straight-forward. In a parallel system it can be very difficult. It requires the explicit modelling of the built-in mechanism which may include such complex mechanisms like queuing of events/messages or an interrupt mechanism for activities. An object which represents its message queues is called meta-object and the modelling style reflective [172].

To perform the transformation vice versa states have to be identified which are modelled by some attributes values and by the protocol of the object. Depending on the set of values which an attribute can contain the resulting state machine may become very large.

So far, we have introduced the term object and we have characterized different views on objects. Corresponding modelling methodologies and languages are object-based if they support the modelling of objects. Such languages allow the decomposition of a system into objects which resemble concepts or objects from the real world. This makes object-based methodologies a good candidate for modelling at system level.

#### 3.1.4 Prototype

In the modelling of a system we very often can identify several objects with the same properties. The objects have the same structure and behaviour. What differs are the actual values of their attributes and their relation to other objects i.e., the concrete context in which they are used. The idea of re-using a description of an object in another context suggests itself. Such an object which can be re-used is called a prototype or exemplar.[104, 106]. A prototype serves as a model for the other objects.

<sup>5.</sup> It is important to note that the state machine here is not necessarily part of the abstraction i.e., the interface of the object.

#### 3.1.5 Class

The next idea is to abstract from the concrete context an object is used. A key concept is the classification of objects with the same properties. Instead of describing a concrete object a class of objects is modelled by describing the common properties of the objects. In this view a class is a set of objects with the same structure and behaviour. The description of a class is a meta-model which serves as a template for objects. Although this sometimes might be a little bit confusing such a meta-model is also called class. A class has the ability to generate objects or instances. An instantiation declares an object to belong to a certain class and probably to have a name.

A class consists of an interface and may consist of an implementation. They describe the interface and implementation of the respective object. A class which does not have an implementation of its operations is called *abstract class* as it only provides an abstraction of its behaviour. It is obviously not possible to directly generate an instance of an abstract class. As we shall see later on an abstract class may be used to describe the common properties of a set of classes.

The class concept allows to abstract the relations between objects by modelling relations between classes. Again, the basic relation between classes is the clientship. The variants of the relations between classes are analogue to the relations of objects.

A has-a relation between objects is abstracted by a has-a relation between classes. Similar to objects the structure which implements the relation is modelled by attributes. However, the attribute is not an object or a container of an object but a template of it. A class not only abstracts the services its objects provide it also has to describe the services they require. This leads to the notion that certain classes of objects are characterized not merely by services they provide but also by services they require at the same level of abstraction from other objects [17].

A difficult problem in that context is the abstraction of the distribution boundaries. If a class requires a service of an object which is not part of the class's structure to implement its behaviour an abstraction of that object is necessary which can be replaced in various contexts by the required object. There are various different solutions to that problem in different methodologies and languages. The common principle is to use a kind of interface as abstraction of the required object and to link the interface in an instantiation to a concrete object. The interface is part of the client object and abstracts a server object outside the client and makes it visible from within the client. A more complex situation occurs if the modelling methodology or language allows a link to change dynamically during the execution of the model. The link is typically modelled by a reference mechanism, i.e. by pointers. In such a case the message passing mechanism does not use a static object name to address an object but the reference. A state variable which might store such a reference is called *instance variable*.

An assignment of a new reference to an instance variable might be the result of an operation's execution. Then the operation dynamically changes the distribution boundaries of an object. The unpleasant thing is that the interface no longer abstracts the services an object requires although this might characterize a class as mentioned above.

The advantage of modelling relations between objects by instance variables is the flexibility to modify the relations during the execution of the model. It is even possible to allow the generation of new objects during the execution and to identify them by references which are generated simultaneously to the object. The concept allows for example, to model a use-relation by an instance variable in a client which references the server object. The operations of the server are invoked by messages sent via the reference. Although storing the reference in an instance variable might at first glance look like a has-a relation it is a use-relation because any other clients may contain references to the same server object. To design a class which contains a reference to a server as an instance variable it might be useful to have an abstraction of the server. It might be possible that at that point of time in the design process the corresponding implementation of the server does not exist. If the modelling methodology allows to model the implementation of a class after its abstraction was used in other classes we call such a technique deferred implementation of classes.

### **3.2 Object-Oriented Modelling**

As mentioned above, relationships between objects dynamically may change e.g. by instance variables which refer to different objects during the execution of a model, i.e. during run-time. The objects may belong to different classes which use the same abstraction of an operation for different implementations. The particular implementation of the operation which will be executed if a message via the instance variable requests the execution of the operation depends dynamically on the class of the object. The request is dynamically bound to a particular operation implementation. We call such a mechanism *dynamic binding* or *late binding*. The benefit of such a technique is that a client is not required to care about possible variants in the implementation of operations of the server. The abstraction of the server is *polymorphic* with respect to the client. The ability to distinguish different classes of a server object at run-time and to execute the corresponding operation is called *dynamic polymorphism*<sup>6</sup>.

The concept is different from genericity which also may provide a technique to model polymorphic objects. Genericity allows to model polymorphic objects by passing the corresponding class descriptions as generic parameters to the model before the execution of the model. During the execution of the model the parameter i.e. the class of an object must not change it is static. We say that genericity provides *static polymorphism*.

Also different from dynamic polymorphism is static operation overloading. An important difference between operation overloading and dynamic binding is that the implementation of an overloaded operation has to be statically determined before the execution of the model (i.e. at compile time). Thus, overloading is not appropriate to model dynamically changing relationships between objects.

#### **3.2.1 Polymorphism**

Polymorphism which allows any server to be used in a use-relation of a client allows very flexible modelling. However, there is no guarantee that a server provides the operation which is requested by a message from a client. Such a situation is a run-time error. It is not feasible to rule out such a situation during the modelling. It is only possible to detect such an error during run-time and to initiate some error recovery mechanisms, e.g., to signal an error and to perform a nop operation.

If such a behaviour is not acceptable a modelling methodology or language has to be used which puts some constraints on the use of polymorphism which can be checked at compile time. The constraints are required to guarantee messages are only sent to servers which provide the requested operation. The constraints are imposed by a strong typing.

<sup>6.</sup> We very often only refer to polymorphism, if we actually mean dynamic polymorphism.

#### 3.2.2 Typing

A type is a set of entities that share the same features with respect to a certain aspect in modelling. A predicate is used to describe the features. In some languages it is possible to split up a type a so called parent type into sub-sets which are called subtypes. A stronger predicate which consists of the parent type's predicate and additional constraints describes the features of the sub-type.

If an entity in a model is assigned a type the predicate can be used to interpret the information which the entity contains. The interpretation can be performed statically at compile time. This allows to detect modelling errors in which misinterpretations of information may occur. In other words, it can be avoided that an entity is expected to have a feature which it does not have. The situation is slightly different if a subtype concept is used. The information which the entity of a subtype contains, i.e. its value can be used in any context where the information is expected which is interpreted as the parent type. However, the other way around it is not possible to use any arbitrary value of a parent type in the entity of a subtype. The value may not meet the additional constraints. The problem is that there is no mechanism to generally detect such a situation at compile time. It only can be detected and handled as run-time error.

The concept to make polymorphism more secure is to assign a type to each object and its references, i.e. instance variables. There are several ideas what might be useful features shared by the objects of the same type.

#### 3.2.3 Behavioural compatibility

One idea is that the objects share their properties, i.e., they all have the same behaviour from a client's point of view. The objects may have different implementations of their behaviour but that is not visible for a client in a certain modelling context. Objects of the same type are behaviourally compatible [171]. Polymorphism is restricted to different implementations of the same behaviour. It is possible to predict at compile time what behaviour can be expected by sending a message to an object of a certain type, for example, via a typed instance variable. While the idea is the most advantageous from a security point of view, in most cases it is too difficult to prove the compatibility. Another problem is that behavioural compatibility places strong constraints on polymorphism which may run contrary to the goal of polymorphism to support the modification and extension of objects and classes without modification of their clients.

#### 3.2.4 Compatibility by conformance

Therefore another idea is to have a notion of compatibility which uses weaker constraints. It follows the concept of *conformance* [17]. A class conforms to another class if it can be used in all contexts where the other is expected. It can accept and understand all the messages handled by the other, in other words, it is able to use the same protocol. That means for the type concept that objects of the same type share the same protocol.

It is possible to work out a set of conditions which interfaces of conform classes must meet. An approach is to deduce conformance between classes from special relations between assertions which are part of the interface [64]. A class B conforms to a class A if B subsumes the operations of A and if the following conditions are met: The invariants of B imply the invariants of A. For each operation of A the precondition of A implies the precondition of B and the postcondition of B implies the postcondition of A. This definition assumes that for each operation of A the corresponding operation of B has the same interface, i.e, the same argument list.

It is possible to relax this assumption. To conform it is only required that each argument of an operation of A conforms to the corresponding argument of the operation of B. The rule is called *contra-variant rule*<sup>7</sup>. Each message which calls an operation of A and passes a parameter to the operation can be understood by B and the parameter can be used as an argument in B because the parameter conforms to the argument, i.e., it can be used in the new context of B.

The sketched type concept allows two objects of the same type to have different implementations. The problem with that concept is that in parallel system design parts of the protocol may be modelled by the implementation (compare Section 3.1). Depending on the complexity and the view of the object it can be quite difficult to answer the question if two implementations obey the same protocol.

#### 3.2.5 Signature compatibility

The third idea starts from the assumption that it is often sufficient to approximate the behaviour of an object or class by its signature and to demand the compatibility of the signatures [171]. By *signature* we mean the syntactic structure of an object's or class's interface<sup>8</sup>. Signatures are compatible if one

<sup>7.</sup> In a language context this rule is normally defined in terms of inheritance (see below)

signature subsumes the other. In other words, the number and profiles of the operations in the interface of one class can be completely found in the interface of the compatible class. Compared to the previous notion of compatibility this approach only takes a part of the protocol into account<sup>9</sup>. Compatibility only depends on the interfaces. Two objects of the same type may have completely different implementations. Signature compatibility does not guarantee the same behaviour of compatible objects or classes nor does it guarantee that they follow the same protocol. It only means that if a message invokes a service in an object there is also a service in a compatible object which can be invoked by the same message.

Each of the presented compatibility concepts establishes a subtype relation on classes. If class B conforms class A then we can think of B as a subtype of  $A^{10}$ . If two objects conform to each other then they are of the same type.

#### 3.2.6 Inheritance

As mentioned above, polymorphism can be used to allow modifications and extensions of server objects without affecting clients. The mechanism to construct such modified and extended objects is *inheritance*. Polymorphism and inheritance are the concepts which make object-based modelling methodologies and languages object-oriented.

Inheritance means mechanisms for sharing common information of classes by allowing new classes to re-use parts of existing classes. We call such a new class *child* and the existing one from which parts are re-used *parent*. We say the child inherits from its parents. If a child is allowed to inherit properties from more than one class we talk about multiple inheritance. Inheritance sets up an *is-a relation* between parent and child. The child itself may become a parent of another child. The is-a relations between a parent and its descendants form an *inheritance hierarchy*.

<sup>8.</sup> We also sometimes use the term signature to denote the syntactic structure of an operation's interface.

<sup>9.</sup> Considerations of a protocol which depends on an implementation are omitted in [17]. Discussions about assertions as part of the interface are omitted as well. Therefore conformance is mistakenly not distinguished from signature compatibility.

<sup>10.</sup> We shall see later on that there might be also some kind of indirect subtype relation between the classes instead of the direct relation *class B is a subtype of class A*.

An inheritance mechanism defines how a new class can be modelled by incremental modification of an existing one. The central question of such a mechanism is what kind of information i.e. which parts of a model can be inherited by a class. As we shall see, the answer is a weighing up of flexibility of modification and preserving the encapsulation of a parent class and thus a matter of modelling philosophy.

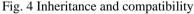

# 3.2.7 Inheritance and compatibility

One philosophy is to use inheritance mechanisms which guarantee the compatibility between child and parent. In other words, the idea is to use a mechanism which automatically makes a child a subtype of a parent. Deriving a child does not affect any client of a parent's object. An object of a child can be used in any context where an object of a parent can be used. Such a polymorphic object may contain any object of a class which is derived from the parent including the parent itself. We call such an object *heterogeneous object container*.

In software programming such containers very often are modelled as references to objects of a sub-tree in an inheritance hierarchy. It is then not the class itself but rather the references which indirectly establish the subtype relation.

A similar indirect<sup>11</sup> approach is to introduce a new kind of classes to model heterogeneous object containers. In a typed class concept we call such a new class *class-wide type*. For each class there is an associated class-wide type and vice versa. The objects of the class-wide type are all objects of the associated class and all classes derived from it. Thus, a class-wide type associated with a parent allows the explicit modelling of a context where objects of any child can be used if it is compatible to the parent. In such an approach the subtype relation is established between the child and the parent's class-wide type.

As discussed in the previous section there are different notions of compatibility. Depending on these notions there are various approaches which claim to preserve the compatibility.

<sup>11.</sup> Indirect with respect to the subtype relation between the child and its parent.

## 3.2.8 Delegation

A very restrictive approach which tries to preserve behavioural compatibility is to use delegation as an inheritance mechanism. *Delegation* means that a child inherits all the properties of a parent. An instantiation of a child consists of instantiations of its parents and a part which models additional structure and behaviour. An interface of a child subsumes all operations of its parents. If a message which invokes an inherited operation is sent to an object of a child it forwards the message to the instantiation of the parent which has the corresponding operation. The is-a relation becomes more a has-a relation in which a parent is an exclusive sub-object. The difference between delegation and a true has-a relation is that delegation breaks the encapsulation of structure between parent and child. A child has access to the parent's structure to model its operations.