Fakultät II – Informatik, Wirtschafts- und Rechtswissenschaften Department für Informatik

# State-based Timing Analysis for Distributed Systems

Von der Fakultät für Informatik, Wirtschafts- und Rechtswissenschaften der Carl von Ossietzky Universität Oldenburg zur Erlangung des Grades und Titels eines

Doktors der Ingenieurwissenschaften (Dr. Ing.)

angenommene Dissertation von

Dipl.-Inform. Tayfun GEZGIN

geboren am 12.02.1984 in Bremen

Gutachter: Prof. Dr. Achim Rettberg Prof. Dr. Bernhard Josko Prof. Dr. Marco Wehrmeister

Tag der Disputation: 02.10.2017

## Abstract

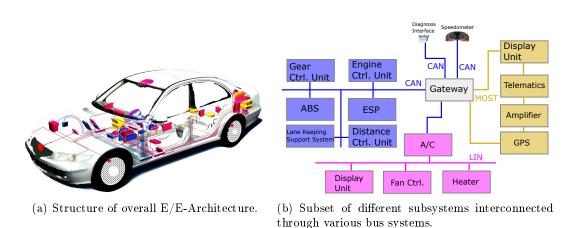

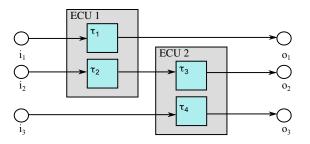

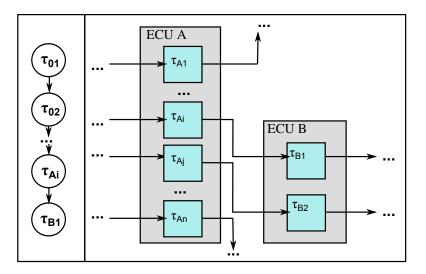

Functionalities of systems in safety-critical domains like the automotive are typically distributed over several computation units. Such systems have to work exactly as specified as a violation of a requirement could result in critical situations and in loss of human life. Error corrections after the start of production of a system could also lead to very high costs. A major aspect of correctness in safety-critical systems is the timeliness of computations. Systems have to finish certain critical computations in a timely manner in order to be safe and reliable. Thus, it is important to have rigorous analysis techniques such as formal verification. Unfortunately, interdependencies among functions and interferences on shared resources complicate the verification of such hard real-time properties. Moreover, changes affecting the specification and the implementation of a system might occur during the design process, which further complicate the verification process, as already performed analyses have to be repeated.

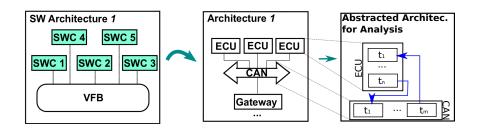

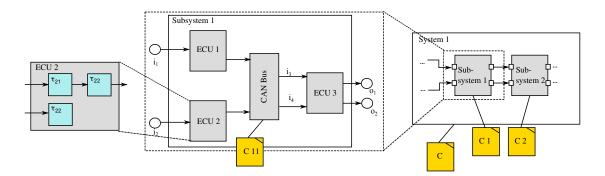

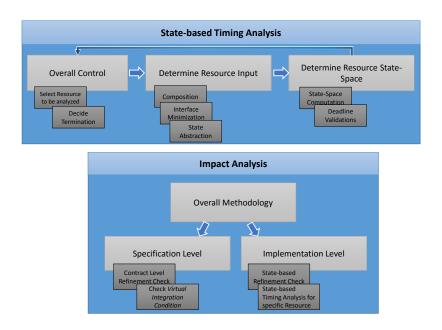

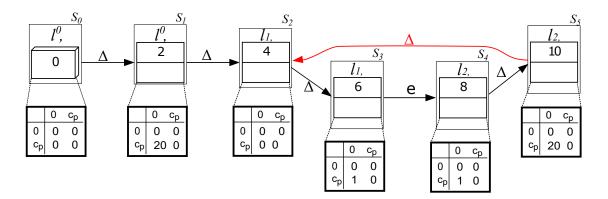

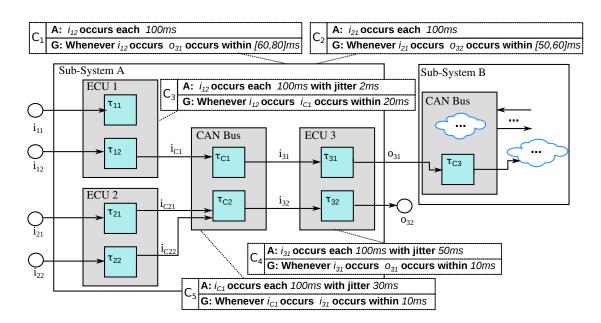

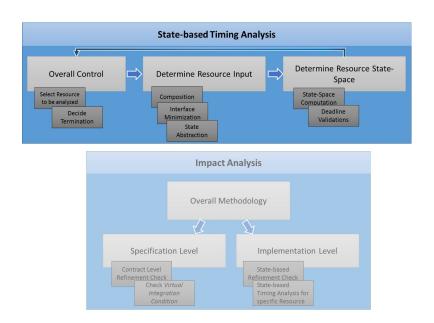

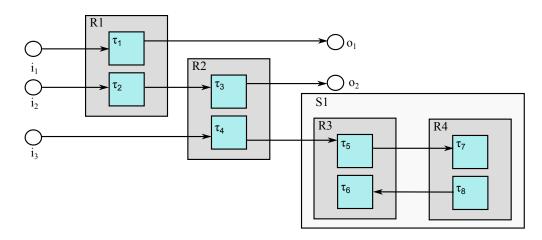

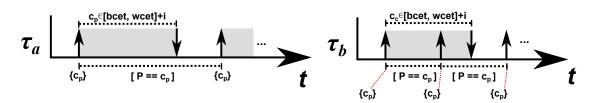

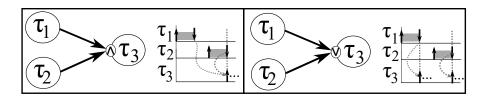

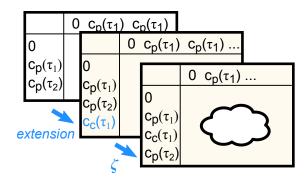

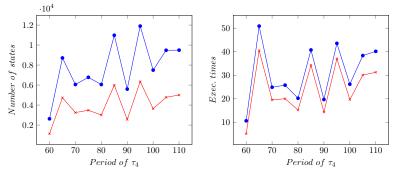

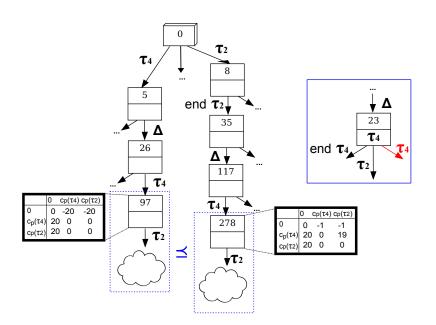

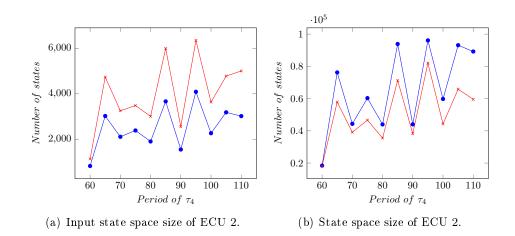

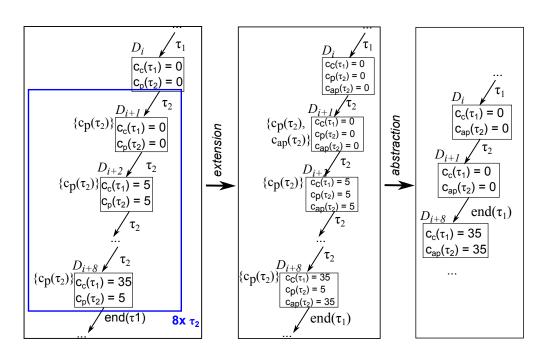

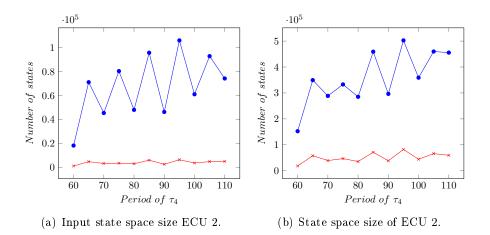

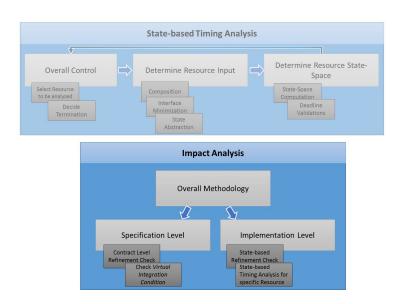

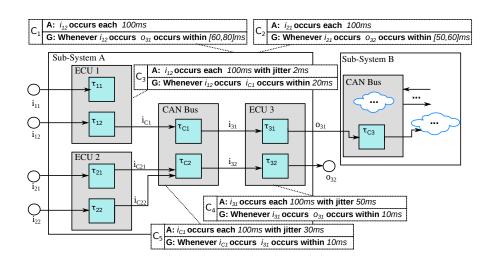

This thesis addresses these problems. A state-based approach for the analysis of timing constraints combining analytic and model checking methods is introduced. In analogy to model checking methods, the full state space for the analysis is taken into account. In classical scheduling analyses only the critical instance of a system is considered, which typically leads to highly pessimistic results. This could lead to expensive systems, as more computation units would be required to satisfy the timing requirements than actually needed. With the approach presented in this thesis exact response times are computed. This results in a reduced demand of computation resources, while guaranteeing that all timing constraints are still fulfilled. In order to alleviate the problem of state space explosion due to state unfolding performed by the presented approach, the state space of an architecture is constructed in an iterative manner. Minimization operations are applied on the interfaces between resources to keep the resulting state spaces as small as possible. To further boost the scalability, abstraction techniques on interfaces between dependent resources are worked out. The effects of the specific abstractions are evaluated with respect to the advantages for scalability and the adequacy of the results.

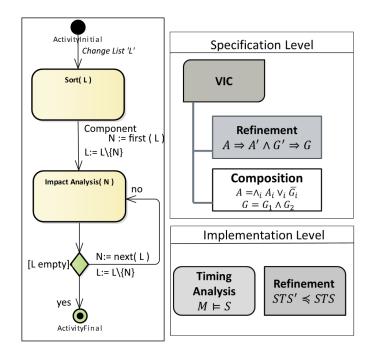

On top of this timing analysis an impact analysis approach is introduced in this thesis to minimize re-verification efforts of timing properties needed when the considered system is modified. Adaptations of the architecture of an already existing and analyzed system could be for instance the addition of new functionalities. Resulting tasks of these new functions could be allocated to existing resources of the system. As verification tasks are typically time consuming it is desirable to minimize the effort of a re-verification and to reuse previous results of analyses which have not been affected by architectural changes. Two abstraction levels are defined which are affected through changes, i.e. the specification level and the implementation level.

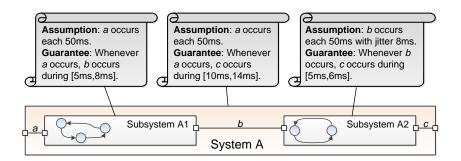

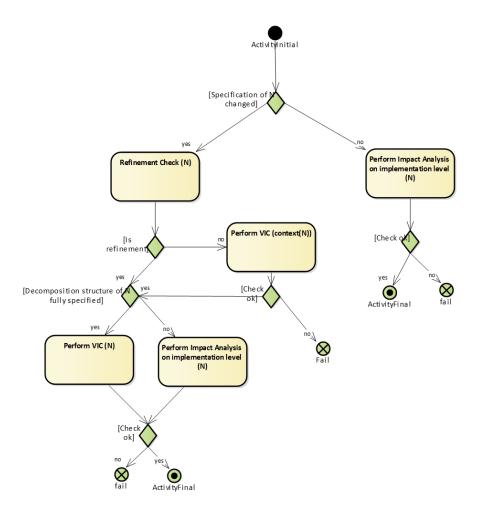

On the specification level contracts are applied and a virtual integration checking technique is introduced. Contracts enable the designer to distinguish between assumed behavior, which must be offered by the environment of the system, and guaranteed behavior, for which the system itself is responsible. Certain characteristics of contracts are used in this thesis to enable a timed automaton-based verification approach. Contracts are specified by using a pattern-based language. An approach is introduced which transforms the language fragments automatically to timed automata. Besides automatically verifying the correct compositions and refinements of parts of a system based on the corresponding contracts, this technique allows to determine the impact of changes on previous analysis results on the specification level. If a contract is changed in such a manner that it refines the previous one, only the internals of the corresponding system have to be re-verified.

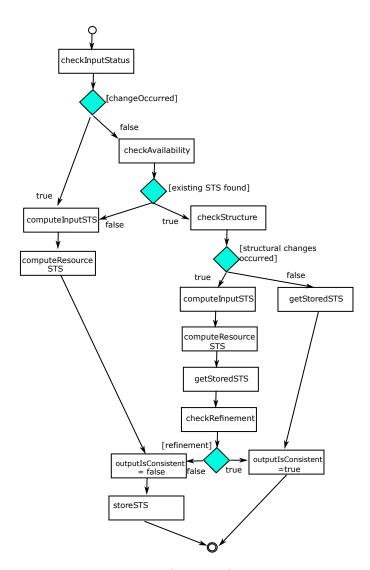

On the *implementation level* a refinement relation between state transition systems of interfaces of components is defined. If a change occurs on a resource the approach is able to determine whether the interfaces to dependent resources are affected. If the interfaces did change in a "good manner" the verification of dependent resources can be omitted, thus saving unnecessary verification times.

In a typical system design process, all introduced concepts are exploited in combination. Therefore, an overall methodology is presented which integrates all introduced verification techniques. Changing a part of a system encapsulating some functionalities implicates the integration of this part into its context, and the re-verification of its adapted implementation against the local specification.

Besides dedicated smaller examples and benchmark systems from related papers, the presented approach is evaluated by the application of an industrial driver assistance system case study.

## Zusammenfassung

Funktionalitäten von Systemen in sicherheitskritischen Domänen wie dem Automobilsektor sind üblicherweise über viele Berechnungseinheiten verteilt. Solche Systeme müssen exakt nach deren Spezifikation arbeiten, da eine Verletzung einer Systemanforderung zu einer kritischen Situation führen und Menschenleben gefährden könnte. Außerdem führen Fehlerkorrekturen nach Produktionsstart zu hohen Kosten. Ein wesentlicher Aspekt von sicherheitskritischen Systemen ist, dass die Berechnungen rechtzeitig erfolgen müssen. Damit solche Systeme sicher und zuverlässig arbeiten, müssen deren Berechnungen rechtzeitig abgeschlossen werden. Deswegen ist es wichtig, dass diese Systeme durch beispielsweise der Anwendung von formaler Verifikation gründlich analysiert werden. Allerdings erschweren gegenseitige Abhängigkeiten zwischen Funktionen des Systems und Interferenzen zwischen verschiedenen Funktionen, die durch den Zugriff auf gemeinsam genutzten Ressourcen entstehen können, die Analysen harter Realzeiteigenschaften. Erschwerend kommt hinzu, dass es während der Systementwicklungsphase zu Änderungen an der Spezifikation und der Implementierung des Systems kommen kann. Bereits durchgeführte Analysen müssen dann wiederholt werden.

Im Rahmen dieser Dissertation werden solche Probleme in der Designphase von Systemen adressiert. In dieser Arbeit wird ein zustandsbasiertes Verfahren zum Analysieren des korrekten Schedulings vorgestellt, das analytische und Model Checking Verfahren kombiniert. Für die Analyse wird analog zu den Model Checking Verfahren der gesamte Zustandsraum berechnet. In klassischen Analysen wird ausschließlich die kritische Instanz eines Systems betrachtet. Dies führt zu pessimistischen Antwortzeiten, was wiederrum zu teureren Systemen führen kann, da mehr Berechnungseinheiten eingeplant werden müssen, um den zu hoch eingeschätzten zeitlichen Anforderungen gerecht zu werden. Mit dem in dieser Arbeit vorgestellten Verfahren können solche Kosten eingespart werden, da exakte Antwortzeiten der Tasks berechnet werden. Model Checking Ansätze haben typischerweise Probleme mit der Skalierbarkeit. Die Zustandsräume werden bereits für kleine Systeme sehr groß. Um dieses Problem zu verringern, wird der Zustandsraum der kompletten Architektur in dem hier vorgestellten Ansatz iterativ berechnet. Die Zustandsräume an den Schnittstellen von abhängigen Ressourcen werden dabei durch spezielle Methoden minimiert. Um die Skalierbarkeit weiter zu erhöhen, werden für solche Zustandsräume weitere Abstraktionstechniken vorgestellt. Die Effekte der einzelnen Abstraktionstechniken werden bezüglich der Zustandseinsparung und der Genauigkeit der erzielten Ergebnisse evaluiert.

Die Timing Analyse wird außerdem mit einer Impact Analyse erweitert, mit der

Re-Verifikationen von zeitlichen Eigenschaften verringert werden sollen. Solche Re-Verifikationen sind durch Änderungen im System erforderlich, die während der Entwurfsphase vorgenommen werden. Beispielsweise werden weitere bisher nicht eingeplante Funktionalitäten hinzugefügt, sodass weitere Tasks auf bereits existierende und analysierte Ressourcen allokiert werden. Da Verifikationsaufgaben typischerweise sehr zeitaufwendig sind, gibt es ein großes Potential Entwicklungszeiten durch das Wiederverwenden von vorherigen Analyseergebnissen, die durch Änderungen nicht beeinflusst worden sind, einzusparen.

Durch Änderungen werden im Wesentlichen die zwei Abstraktionsebenen Spezifikation und Implementierung beeinflusst. Auf der Spezifikationsebene wird eine Technik zur virtuellen Integrationsprüfung auf Basis von Contracts vorgestellt. Contracts ermöglichen es dem Entwickler, zwischen Verhalten, das durch den Kontext geliefert werden muss, und dem, das durch das System garantiert werden muss, zu unterscheiden. Einige charakteristische Eigenschaften der Contracts werden in dieser Ausarbeitung genutzt, um eine auf Timed Automaten basierende Verifikationstechnik zu ermöglichen. Dabei werden Contracts durch eine Pattern-basierte Sprache erfasst. Die einzelnen Pattern werden dann durch das Verfahren automatisch zu solchen Automaten transformiert. Zusätzlich zur Verifikation der korrekten Kompositions- und Verfeinerungsbeziehungen von Teilen des Systems ermöglicht diese Technik Auswirkungen von Spezifikationsänderungen auf bisherige Analyseergebnisse zu ermitteln.

Auf der Implementierungsebene wird eine Verfeinerungsbeziehung zwischen den Zustandsräumen voneinander abhängiger Komponenten vorgestellt. Wenn eine Änderung an einer Ressource durchgeführt wird, ist der vorgestellte Ansatz in der Lage zu entscheiden, ob Schnittstellen zu abhängigen Ressourcen betroffen sind und damit diese neu analysiert werden müssen oder ob unnötige Verifikationszeit eingespart werden kann. Alle vorgestellten Konzepte finden typischerweise im Entwurfsprozess eine kombinierte Anwendung. Deswegen wird in dieser Dissertation eine Methodik ausgearbeitet, die alle vorgestellten Verifikationstechniken integriert. Das Ändern eines Teilsystems führt zu einer Integrationsprüfung zum Restsystem und der Re-Verifikation der internen Struktur oder der geänderten Implementierung. Neben dedizierten, kleineren Beispielen und Benchmark-Systemen aus verwandten Veröffentlichungen wird das hier vorgestellte Verfahren an einer Fallstudie zu einem Fahrerassistenzsystem evaluiert.

# Contents

|    | Intro                          | oductio          | n                                                    | 11                                      |  |  |  |  |  |

|----|--------------------------------|------------------|------------------------------------------------------|-----------------------------------------|--|--|--|--|--|

|    | 1.1.                           | Motiva           | ntion                                                | 11                                      |  |  |  |  |  |

|    | 1.2.                           | Object           | ive of this Thesis                                   | 13                                      |  |  |  |  |  |

|    | 1.3.                           | Contex           | t of this Thesis                                     | 17                                      |  |  |  |  |  |

|    | 1.4.                           | Outlin           | e                                                    | 18                                      |  |  |  |  |  |

| 2. | Fou                            | Foundations 2    |                                                      |                                         |  |  |  |  |  |

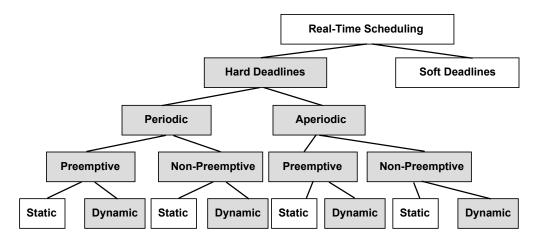

|    | 2.1.                           | Schedu           | lling of Real-Time Tasks                             | 23                                      |  |  |  |  |  |

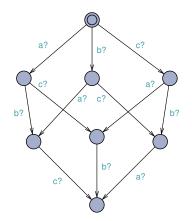

|    |                                | 2.1.1.           | Tasks and Task Dependency Graphs                     | 24                                      |  |  |  |  |  |

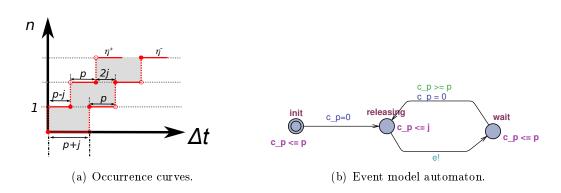

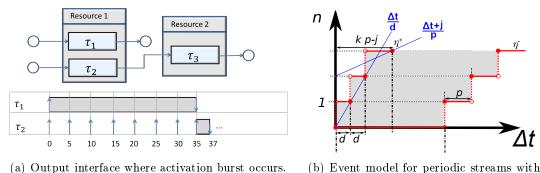

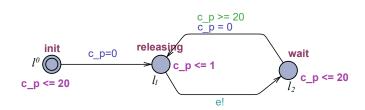

|    |                                | 2.1.2.           | Event Models                                         | 25                                      |  |  |  |  |  |

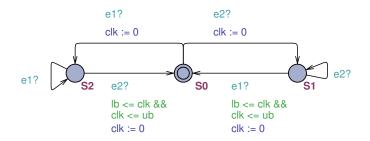

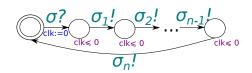

|    | 2.2.                           | Timed            | Languages and Timed Automata                         | 27                                      |  |  |  |  |  |

|    | 2.3.                           | Modeli           | ing of System Architectures                          | 33                                      |  |  |  |  |  |

|    |                                | 2.3.1.           | Components and Resources                             | 33                                      |  |  |  |  |  |

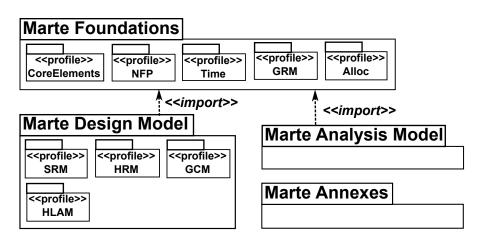

|    |                                | 2.3.2.           | Modeling in MARTE                                    | 36                                      |  |  |  |  |  |

|    | 2.4.                           | Specifi          | cation of Requirements                               | 38                                      |  |  |  |  |  |

|    |                                | 2.4.1.           | Contract-based Design                                | 39                                      |  |  |  |  |  |

|    |                                | 2.4.2.           |                                                      | 44                                      |  |  |  |  |  |

|    | 2.5.                           | Summa            | ary                                                  | 49                                      |  |  |  |  |  |

| 3. | State-based Timing Analysis 51 |                  |                                                      |                                         |  |  |  |  |  |

|    | 3.1.                           |                  | ation                                                | 51                                      |  |  |  |  |  |

|    | 3.2.                           |                  | d Work                                               | 53                                      |  |  |  |  |  |

|    | -                              | 3.2.1            |                                                      | 53                                      |  |  |  |  |  |

|    |                                | 3.2.2.           | Model Checking Approaches                            | 56                                      |  |  |  |  |  |

|    |                                | 3.2.3.           | Combination of Analytical and State-based Approaches | 59                                      |  |  |  |  |  |

|    |                                | 3.2.4.           | Contribution of this Chapter                         | 60                                      |  |  |  |  |  |

|    | 3.3.                           |                  | al Approach                                          | 60                                      |  |  |  |  |  |

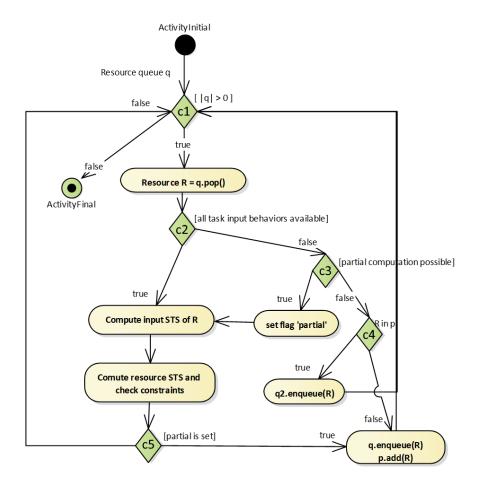

|    |                                | 3.3.1            | Iterative Analysis Approach                          | 61                                      |  |  |  |  |  |

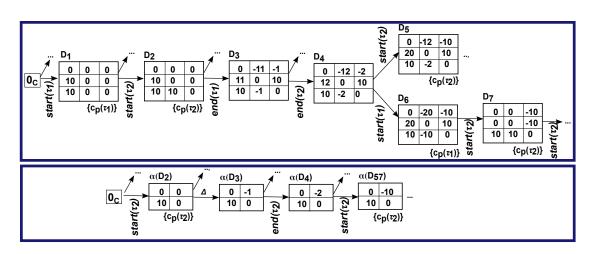

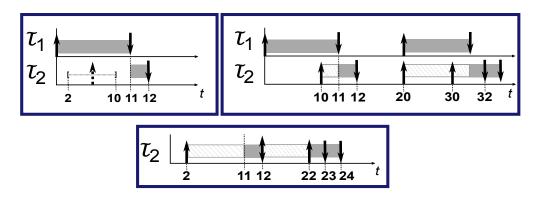

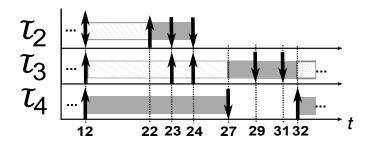

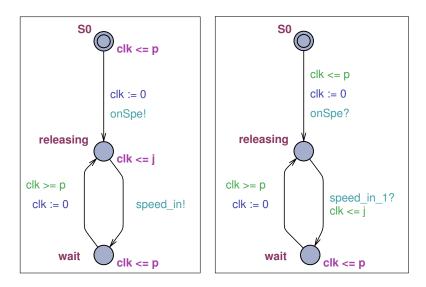

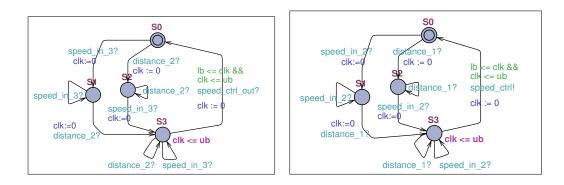

|    |                                | 3.3.2.           | Symbolic Transition Systems of Resources             | 63                                      |  |  |  |  |  |

|    |                                |                  |                                                      |                                         |  |  |  |  |  |

|    |                                | 3.3.3.           | Simplification of Symbolic Transition Systems        | 67                                      |  |  |  |  |  |

|    | 3.4.                           | 3.3.3.<br>Operat | Simplification of Symbolic Transition Systems        | $\begin{array}{c} 67 \\ 70 \end{array}$ |  |  |  |  |  |

|    | 3.4.                           |                  | Simplification of Symbolic Transition Systems        | 67<br>70<br>70                          |  |  |  |  |  |

|    | 3.5.                                                                             | Analys                                                                                                                                                              | sis Algorithm                                                  | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|----|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|    |                                                                                  | 3.5.1.                                                                                                                                                              | Main Analysis Algorithm                                        | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|    |                                                                                  | 3.5.2.                                                                                                                                                              | Successor Computation                                          | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|    |                                                                                  | 3.5.3.                                                                                                                                                              | Completeness and Soundness of Algorithm                        | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|    |                                                                                  | 3.5.4.                                                                                                                                                              | Termination of Algorithm                                       | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|    |                                                                                  | 3.5.5.                                                                                                                                                              | Minimization through Untimed Bisimulation, Timed Simulation    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|    |                                                                                  |                                                                                                                                                                     | Relation                                                       | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|    | 3.6.                                                                             | Abstra                                                                                                                                                              | action Techniques                                              | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|    |                                                                                  | 3.6.1.                                                                                                                                                              | Clock Resets and Duration Clocks                               | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|    |                                                                                  | 3.6.2.                                                                                                                                                              | Clocks of Interface STSs                                       | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|    |                                                                                  | 3.6.3.                                                                                                                                                              | Abstraction through Simulation Relation                        | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|    |                                                                                  | 3.6.4.                                                                                                                                                              | Effects of Over-Approximations for Iterative Analysis Approach | 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|    |                                                                                  | 3.6.5.                                                                                                                                                              | Testing: Abstraction through Under-Approximation               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|    |                                                                                  | 3.6.6.                                                                                                                                                              |                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

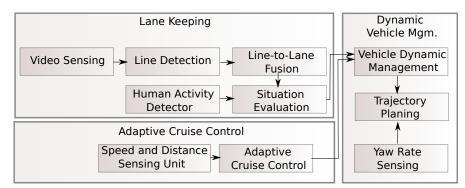

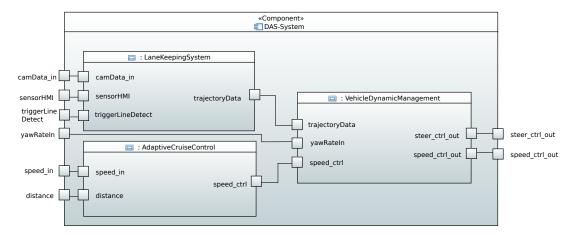

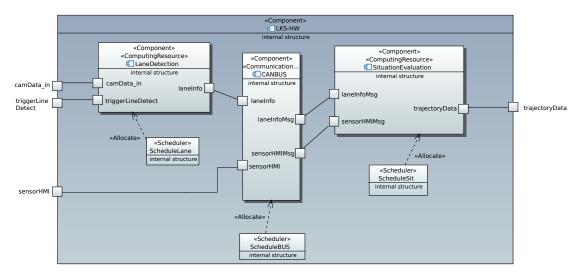

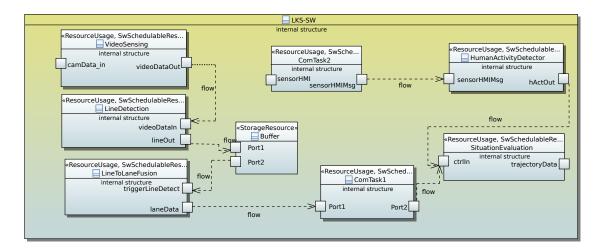

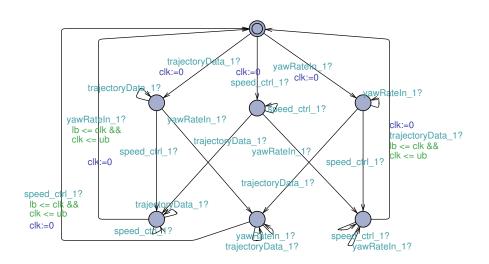

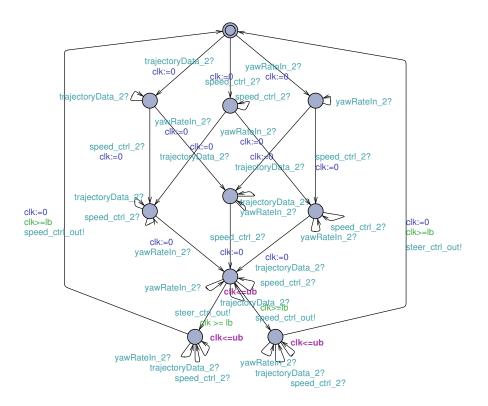

|    | 3.7.                                                                             |                                                                                                                                                                     | Study: Driver Assistance System                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|    |                                                                                  | 3.7.1.                                                                                                                                                              | -                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|    |                                                                                  | 3.7.2.                                                                                                                                                              |                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

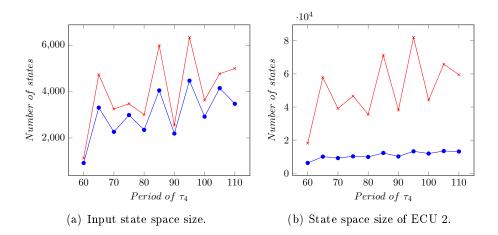

|    |                                                                                  |                                                                                                                                                                     | Evaluation Results                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|    |                                                                                  |                                                                                                                                                                     | Observation on Scalability                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|    | 3.8.                                                                             | $\operatorname{Summ}$                                                                                                                                               | ary                                                            | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|    | . Contract-based Impact Analysis 1                                               |                                                                                                                                                                     |                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 4. | Con                                                                              | tract-b                                                                                                                                                             | ased Impact Analysis                                           | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |