Fakultät II – Informatik, Wirtschafts- und Rechtswissenschaften Department für Informatik

# State-Based Real-Time Analysis of Synchronous Data-flow (SDF) Applications on MPSoCs with Shared Communication Resources

Dissertation zur Erlangung des Grades eines Doktors der Ingenieurwissenschaften

vorgelegt von

M.Sc. Maher Fakih

Gutachter:

Prof. Dr. Achim Rettberg

Prof. Dr. Marcio Eduardo Kreutz

Tag der Disputation: 11.07.2016

# **Abstract**

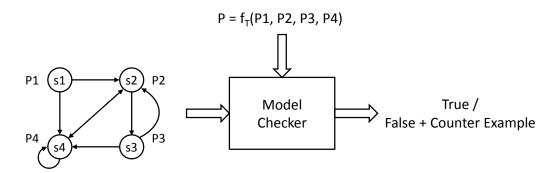

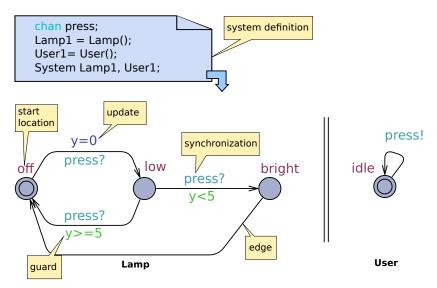

The growing computational demand of real-time applications (in automotive, avionics and multimedia) requires extensions in the traditional design process to support Multi-Processor System-on-Chip (MPSoC) architectures. Due to their significantly increased performance and Space Weight and Power (SWaP) reductions, MPSoCs offer an appealing alternative to traditional single-processor architectures. The timing analysis of hard real-time applications running on MPSoC platforms is much more challenging compared to traditional single processor. This comes from the large number of shared processing, communication and memory resources available in today's MPSoCs. Yet, this is an indispensable challenge for enabling their usage with hard-real time systems in safety critical application domains (e.g. avionics, automotive). In this thesis, a statebased real-time analysis methodology for a subset of data-flow oriented applications using model-checking is proposed. Applications are represented as Synchronous Data Flow (SDF) graphs, the MPSoC is represented as Architecture Resource Graph (ARG) and a mapping relation between these graphs describes the implementation of the application on the MPSoC architecture. This approach utilizes Timed Automata (TA) as a common semantic model to represent execution time boundaries (best-case and worstcase execution times) of SDF actors and communication FIFOs and their mapping as well as their utilization of MPSoC resources, such as scheduling of SDFGs and shared communication resource access protocols for interconnects, local and shared memories. The resulting network of TA is analyzed using the UPPAAL model-checker for obtaining safe timing bounds of the chosen implementation. The proposed methodology is compared with a state-of-the-art analytical method showing a significant precision improvement (up to a percentage improvement of 300%) compared with the worst-case bound calculation based on a pessimistic analytical upper-bound delays for every shared resource access. Furthermore, the analysis feasibility of our approach was demonstrated for small parallel systems. In addition, the limitations of our approach and abstraction methods to improve scalability were explored. We also demonstrate the applicability of our approach to an industrial case-study using a multi-phase electric motor control application (modeled as an SDFG) mapped to a state-of-the-art MPSoC with both the burst and single-beat inter-processor communication styles.

# Contents

| Co | onten | its         |           |                                     | i  |  |

|----|-------|-------------|-----------|-------------------------------------|----|--|

| 1  | Intr  | ntroduction |           |                                     |    |  |

|    | 1.1   | Conte       | ext and M | lotivation                          | 1  |  |

|    | 1.2   | Resea       | rch Ques  | tions and Contributions             | 5  |  |

|    |       | 1.2.1       | Researc   | h Questions                         | 5  |  |

|    |       | 1.2.2       |           | utions                              | 7  |  |

|    | 1.3   | Thesis      | s Outline |                                     | 9  |  |

|    | 1.4   |             |           | ons                                 | 9  |  |

| 2  | Basi  | ic Cond     | cepts and | Background                          | 11 |  |

|    | 2.1   | Syster      | m Level I | Design (SLD) Methodologies          | 12 |  |

|    | 2.2   | Task I      | Model (M  | Iodel of Computation)               | 15 |  |

|    |       | 2.2.1       | Synchro   | onous Data-flow Graphs (SDFGs)      | 15 |  |

|    |       |             | 2.2.1.1   | Scheduling                          | 16 |  |

|    |       |             | 2.2.1.2   | Timing Properties                   | 19 |  |

|    |       |             | 2.2.1.3   | Expressiveness                      | 21 |  |

|    |       |             | 2.2.1.4   | Clustering Methods                  | 22 |  |

|    |       | 2.2.2       | Simulin   | ık                                  | 23 |  |

|    | 2.3   | Timin       | g Issues  | of MPSoCs                           | 26 |  |

|    |       | 2.3.1       | Process   | or Elements                         | 28 |  |

|    |       | 2.3.2       | Storage   | Resources                           | 29 |  |

|    |       | 2.3.3       | Commu     | unication Resources                 | 30 |  |

|    |       |             | 2.3.3.1   | Scheduling (arbitration)            | 31 |  |

|    |       |             | 2.3.3.2   | Timing models                       | 33 |  |

|    |       | 2.3.4       | Address   | sable Devices                       | 35 |  |

|    |       | 2.3.5       | Inter-Pr  | rocessor Communication (IPC) Styles | 36 |  |

|    |       | 2.3.6       | Predica   | ble Design of MPSoCs                | 37 |  |

|    | 2.4   | Intera      | ction wit | h the Environment                   | 38 |  |

|    | 2.5   | Real-t      | ime Anal  | lysis Methods                       | 38 |  |

ii CONTENTS

|   |      | 2.5.1   | Dynamic Real-time Methods                     | 40 |

|---|------|---------|-----------------------------------------------|----|

|   |      | 2.5.2   | Static (Formal) Real-time Methods             | 41 |

|   |      |         | 2.5.2.1 State-based RT Analysis Methods       | 43 |

|   | 2.6  | Sumn    | nary                                          | 52 |

| 3 | Rela | ated W  | ork .                                         | 53 |

|   | 3.1  | Forma   | al Real-time Analysis Methods                 | 53 |

|   |      | 3.1.1   | •                                             | 54 |

|   |      |         |                                               | 54 |

|   |      |         | 3.1.1.2 SDFAs on MPSoCs                       | 56 |

|   |      |         |                                               | 57 |

|   |      | 3.1.2   | State-based Real-time Analysis Methods        | 58 |

|   |      |         |                                               | 58 |

|   |      |         |                                               | 60 |

|   |      |         |                                               | 61 |

|   | 3.2  | Mode    |                                               | 62 |

|   |      | 3.2.1   | 8                                             | 62 |

|   |      | 3.2.2   |                                               | 63 |

|   |      | 3.2.3   | -                                             | 65 |

|   | 3.3  | Sumn    |                                               | 66 |

|   |      |         |                                               |    |

| 4 | Syst |         |                                               | 67 |

|   | 4.1  | •       | o ,                                           | 58 |

|   |      | 4.1.1   |                                               | 68 |

|   |      | 4.1.2   |                                               | 70 |

|   | 4.2  | ,       |                                               | 73 |

|   |      | 4.2.1   | J                                             | 74 |

|   |      | 4.2.2   |                                               | 75 |

|   |      | 4.2.3   | , , ,                                         | 76 |

|   |      | 4.2.4   | J .                                           | 78 |

|   |      |         | O .                                           | 78 |

|   |      |         | O                                             | 79 |

|   |      | 4.2.5   | Model of Performance (MoP) Extraction         | 31 |

|   | 4.3  | Sumn    | nary                                          | 34 |

| 5 | Stat | e-based | d Real-time Analysis of SDFGs on MPSoCs       | 87 |

|   | 5.1  | Repre   | senting Performance Model as Timed Automata 8 | 88 |

|   | 5.2  | Imple   | 1                                             | 90 |

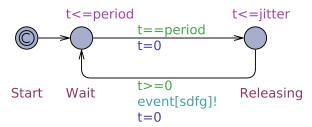

|   |      | 5.2.1   | Event Trigger Template                        | 90 |

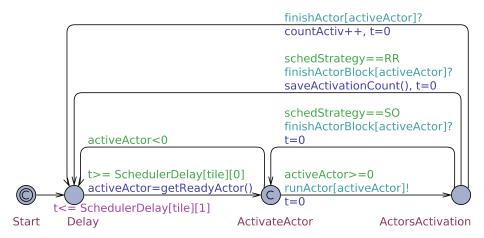

|   |      | 5.2.2   | 1                                             | 91 |

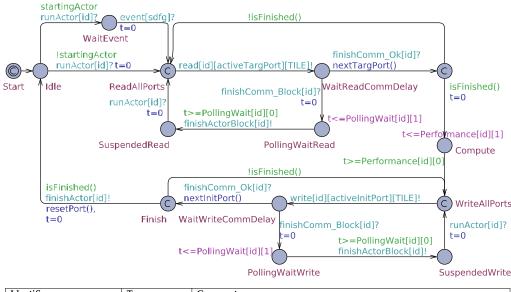

|   |      | 5.2.3   | 1                                             | 92 |

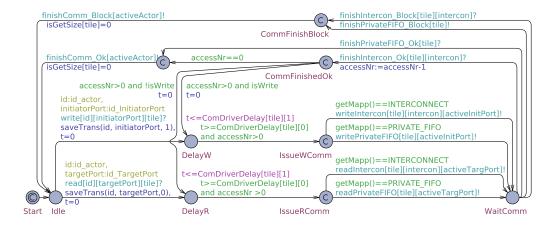

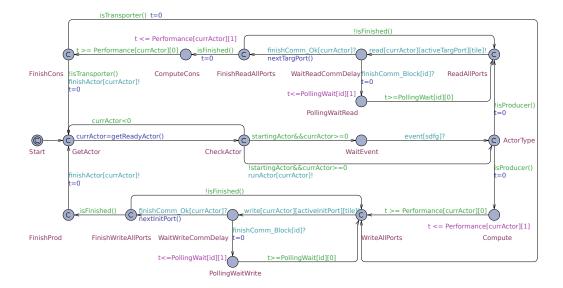

|   |      | 5.2.4   | Communication Driver Template                 | 94 |

CONTENTS

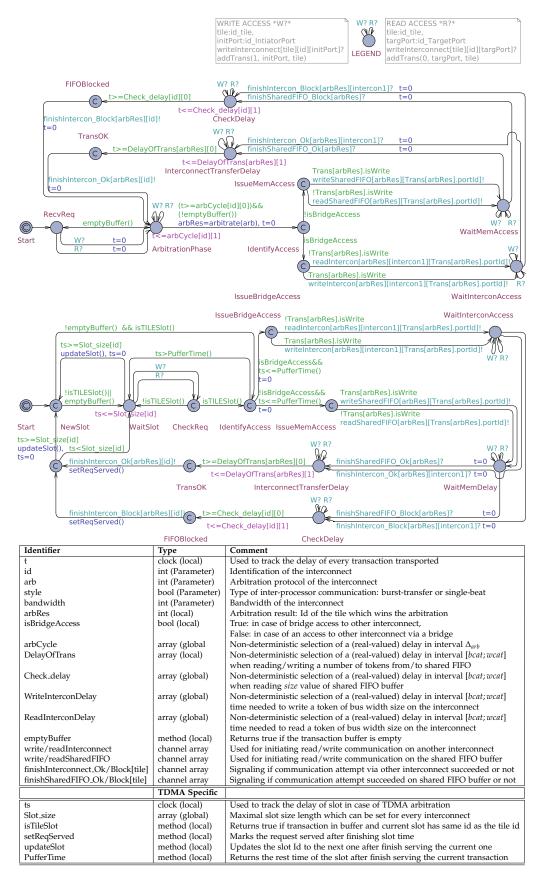

|   |      | 5.2.5   | Shared Interconnect Templates                             | 95  |

|---|------|---------|-----------------------------------------------------------|-----|

|   |      | 5.2.6   | Templates of Shared and Private FIFO Buffers              | 99  |

|   |      | 5.2.7   | Extensions for DMA Burst Transfer                         | 100 |

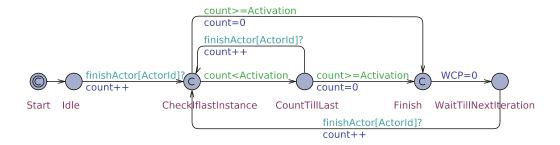

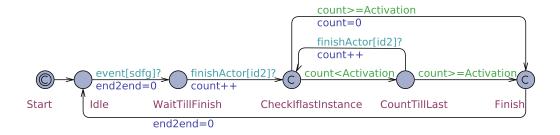

|   |      | 5.2.8   | Observer TA Templates for Real-time Analysis              | 101 |

|   | 5.3  | Real-t  | ime Analysis via Model-checking                           | 103 |

|   | 5.4  | Metho   | ods for Improving Scalability                             | 104 |

|   |      | 5.4.1   | Optimizing the Implemented Timed-automata Templates       | 105 |

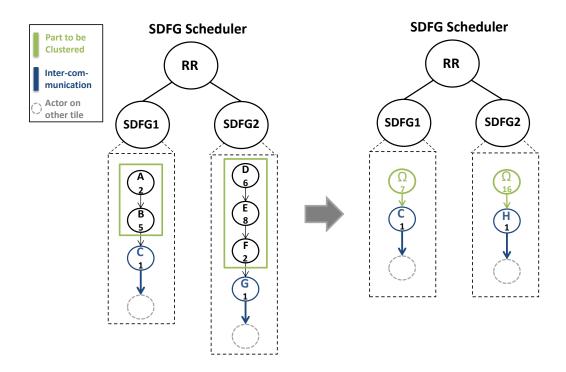

|   |      | 5.4.2   | Applying Clustering Method                                | 107 |

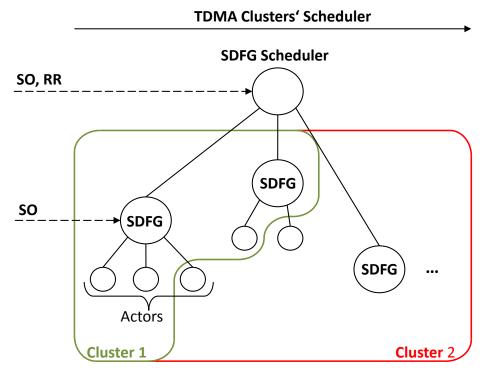

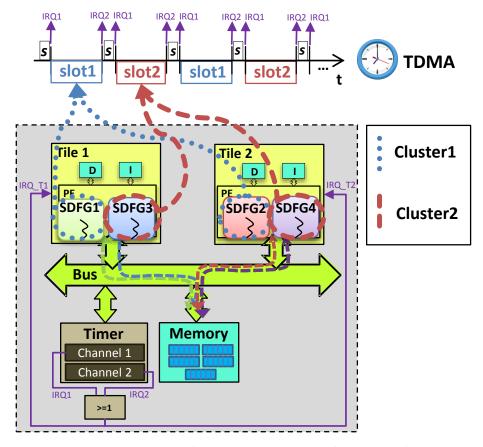

|   |      | 5.4.3   | Temporal and Spatial Segregation for a Composable and     |     |

|   |      |         | Scalable RT Analysis                                      | 109 |

|   | 5.5  | Sumn    | nary                                                      | 113 |

| 6 | Mod  | del-bas | ed Design Flow for RT-Analysis of Embedded Applica-       |     |

|   | tion | s on M  | IPSoCs                                                    | 115 |

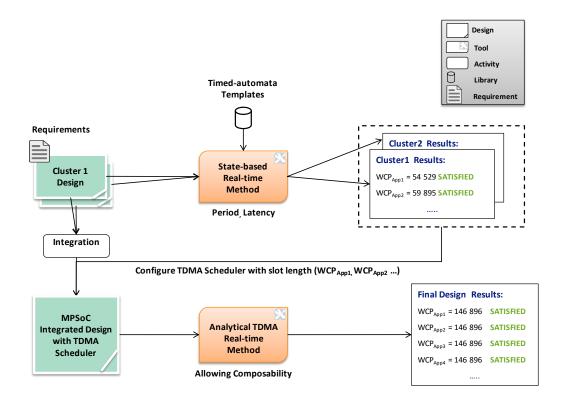

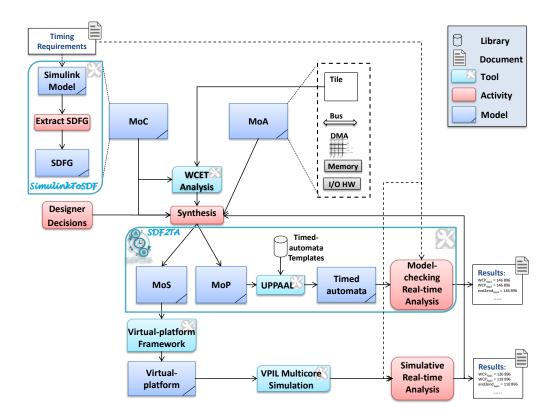

|   | 6.1  | Mode    | l-based Design Flow Overview                              | 116 |

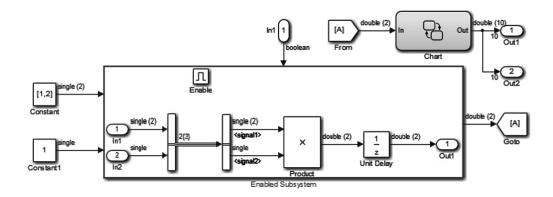

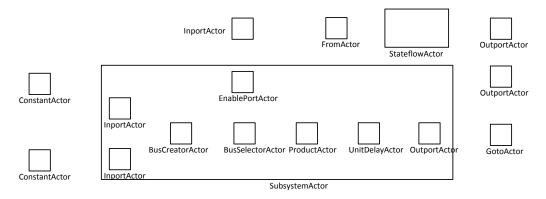

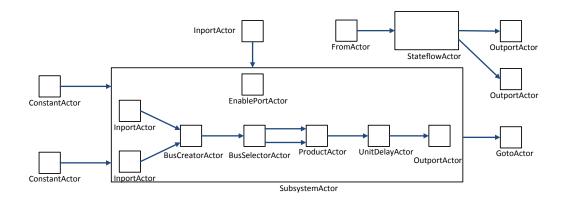

|   | 6.2  | Simul   | ink to SDFGs Translation                                  | 118 |

|   |      | 6.2.1   | Constraints on the Simulink Model                         | 120 |

|   |      | 6.2.2   | Translation Procedure                                     | 121 |

|   | 6.3  |         | mation of our State-based RT Approach                     | 126 |

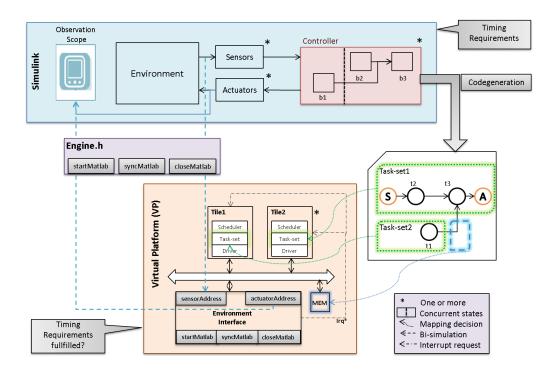

|   | 6.4  | Virtua  | al-Platform-in-the-Loop Simulation for MPSoCs             | 128 |

|   |      | 6.4.1   | Motivation                                                | 128 |

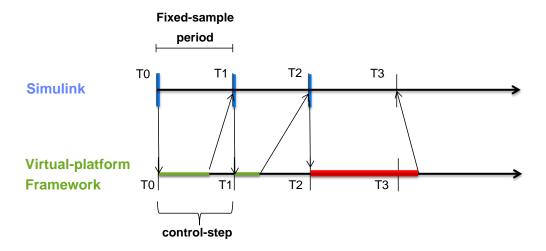

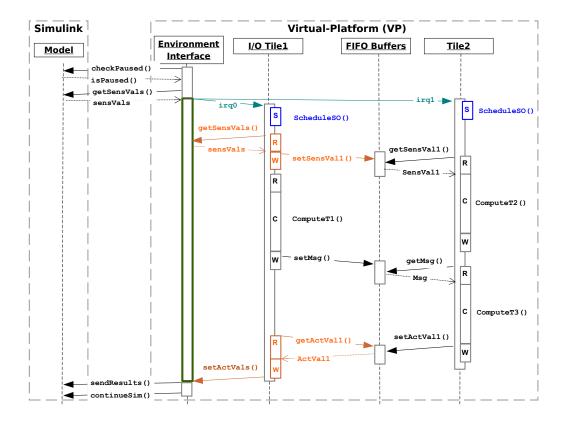

|   |      | 6.4.2   | Bi-simulation Procedure                                   | 129 |

|   | 6.5  | Imple   | mentation Concepts                                        | 134 |

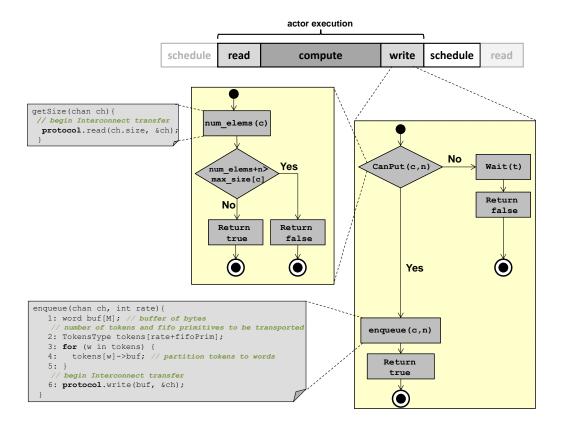

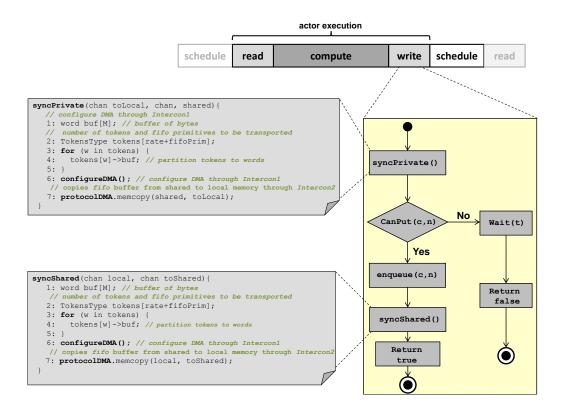

|   |      | 6.5.1   | Pseudo-code of Static-order Scheduled SDFG                | 134 |

|   |      | 6.5.2   | Pseudo-code of SDFGs Schedulers                           | 135 |

|   |      | 6.5.3   | Communication Driver Issues                               | 135 |

|   | 6.6  | Sumn    | nary                                                      | 143 |

| 7 |      | luation |                                                           | 145 |

|   | 7.1  |         | asing Confidence in Correctness of Approach               | 145 |

|   | 7.2  |         | ation of Scalability                                      | 152 |

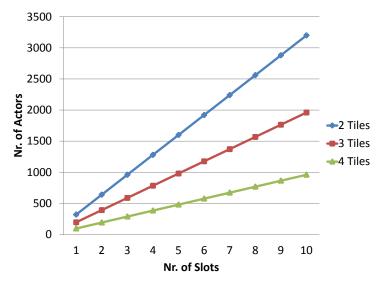

|   |      | 7.2.1   | Possible Scalability w.r.t number of Tiles and Actors     |     |

|   |      | 7.2.2   | Scalability w.r.t Arbitration Protocols                   | 154 |

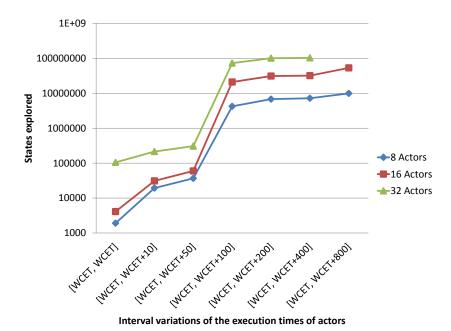

|   |      | 7.2.3   | Scalability w.r.t BCET/WCET Interval Variation            | 155 |

|   |      | 7.2.4   | Possible Scalability Improvement with Actors' Clustering  | 157 |

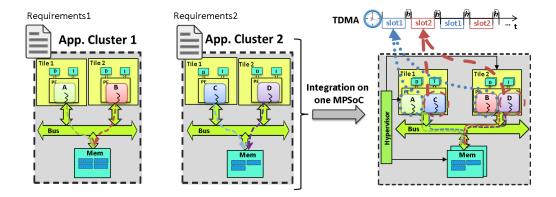

|   |      | 7.2.5   | Possible Scalability Improvement via Temporal Segregation |     |

|   | 7.3  |         | ation of Tightness Improvement                            | 161 |

|   | 7.4  |         | trial Applicability: Motor Control Case-Study             | 164 |

|   |      | 7.4.1   | Motor Control Simulink Model                              | 165 |

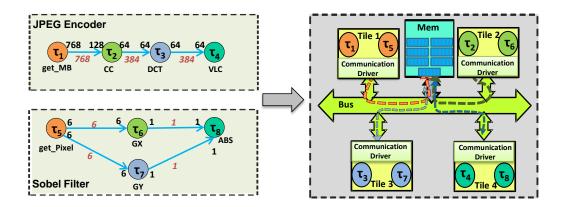

|   |      | 7.4.2   | Motor Control Simulink Model to SDFG Translation          | 165 |

|   |      | 7.4.3   | Aurix TriCore platform                                    | 167 |

|   |      | 7.4.4   | Mapping                                                   | 169 |

iv CONTENTS

|     |         | 7.4.5    | BCET/WCET Analysis of Software Components on single   |     |

|-----|---------|----------|-------------------------------------------------------|-----|

|     |         |          | PEs                                                   | 172 |

|     |         | 7.4.6    | VPIL Simulation for Aurix TriCore                     | 174 |

|     |         |          | 7.4.6.1 Simulation Results                            | 175 |

|     |         | 7.4.7    | SDF2TA RT Results with different Communication Styles | 178 |

|     |         | 7.4.8    | Discussion                                            | 179 |

|     | 7.5     | Summ     | nary                                                  | 180 |

| 8   | Con     | clusior  | and Outlook                                           | 183 |

|     | 8.1     | Discus   | ssion                                                 | 185 |

|     | 8.2     | Future   | e Work and Open Questions                             | 186 |

| Bi  | bliog   | raphy    |                                                       | 191 |

| A   | SDF     | 2TA To   | ool                                                   | 209 |

|     | A.1     | Corre    | ctness of SDF2TA Implementation                       | 209 |

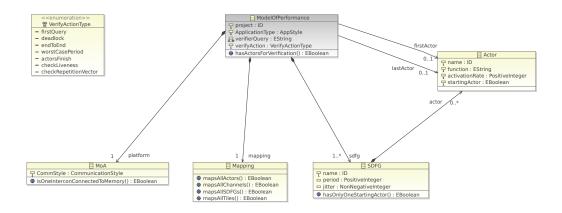

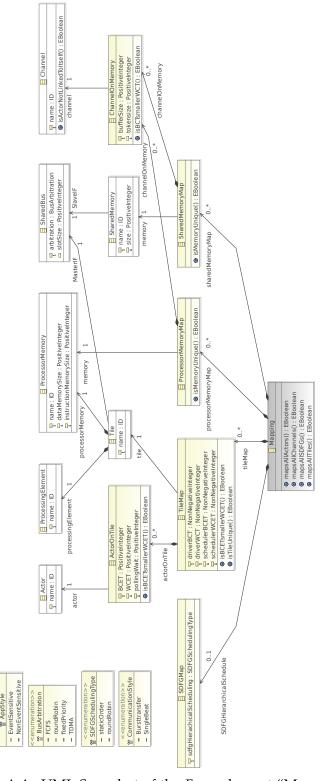

|     | A.2     | SDF27    | TA Ecore model                                        | 210 |

|     |         | A.2.1    | SDFG Ecore element                                    | 211 |

|     |         | A.2.2    | Model of Architecture Ecore Element                   | 212 |

|     |         | A.2.3    | Mapping Ecore Element                                 | 214 |

| В   | Aur     | ix TriC  | ore Experiment                                        | 217 |

|     | B.1     | Simul    | ation Measurements                                    | 217 |

|     |         | B.1.1    | Single-beat Transfer Measurements                     | 218 |

|     |         | B.1.2    | DMA-based Burst Transfer Measurements                 | 219 |

|     | B.2     | Abstra   | actions and Annotations for the MoP                   | 220 |

|     |         | B.2.1    | DMA-based Burst Transfer                              | 220 |

|     |         | B.2.2    | Single-beat transfer through SRI                      | 221 |

| Lis | st of   | Abbrev   | riations                                              | 225 |

| Gl  | ossaı   | <b>y</b> |                                                       | 227 |

| Lis | st of   | Figures  |                                                       | 233 |

| Lis | st of ' | Tables   |                                                       | 235 |

## Chapter 1

# Introduction

### 1.1 Context and Motivation

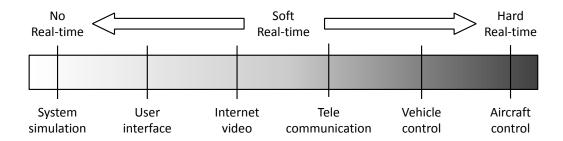

The last decade witnessed a significant technological revolution of miniaturization technologies of processing devices leading to ubiquitous computing and the wide-spread of embedded systems<sup>1</sup> in our everyday life. For instance, a look at a modern car in the automotive domain, shows that a premium version can have about 70 ECUs (embedded devices) on which hundreds of realtime applications are run [Buttle, 2012] and the trend is going towards a larger number of ECUs with more complexity. Depending on their domain of usage, the timing criticality of applications running on such systems can vary from hard real-time systems (e.g. aircraft control or video-processing applications used in safety-critical automotive systems to detect pedestrians crossing or the street signs) where a violation of the real-time requirement can lead to catastrophic results, to non real-time applications (such as an MP3 player in the infotainment domain) where the harmfulness by a violation is very limited. In order to guarantee the safety of hard-real time systems, a real-time (RT) analysis method is indispensable to validate the fulfillment of their hard real-time requirements. According to safety standards like DO-178B/DO-178C [Aeronautical Radio, 1992], ISO-26262 [ISO26262, 2011], IEC-61508 [IEC, 2010], or CENELEC EN-50128 [EN50128, 2009] the functional safety of the software must be demonstrated with respect to the specified requirements and the absence of critical non-functional hazards (including timing hazards in real-time systems) has to be shown [Kästner Daniel and Christian, 2014].

Because of the growing computational demand of such real-time applications (in automotive, avionics and multimedia), the need for more powerful,

<sup>&</sup>lt;sup>1</sup>According to [Marwedel, 2010] an embedded system is defined as: "Embedded systems are information processing systems embedded into enclosing products."

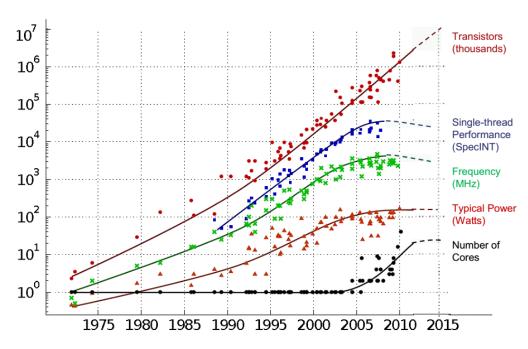

Original data collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond and C. Batten Dotted line extrapolations by C. Moore

Figure 1.1: Trend towards MPSoCs' design (taken from [Fuller and Lynette I. Millett, 2011])

fast and efficient hardware architectures is emerging. In the last decade, the chip industry was faced with the challenge that the chip clock frequencies (as seen in Fig. 1.1 green, x-curve) couldn't be increased without drastically increasing power consumption (as seen in Fig. 1.1 red,  $\triangle$ -curve) and heat wastage. The above phenomena called "clock-racing" (also called frequency scaling) reached its limit at the end of year 2003 (as seen in Fig. 1.1 green, x-curve), while the number of transistors continued to increase (according to Moore's law number of transistors doubles every two years as seen in Fig. 1.1 red,  $\circ$ -curve). This made the extension of current design process for supporting MPSoC architectures inevitable. Due to their significantly increased performance and their Space Weight and Power (SWaP) reductions (see stable power consumption in Fig. 1.1 red,  $\triangle$ -curve, beginning at the end of 2003 as the number of cores was increased), MPSoCs offer an appealing alternative to traditional architectures.

Nevertheless, with MPSoCs emerging, their validation process is becoming a bottleneck. According to [Tang and Wu, 2014], the number of verification engineers needed for nowadays MPSoCs' projects is wide more than the number of design engineers reaching a ratio of 2:1 or even 3:1 the fact which can lead to high costs in the development process. Especially in the real-time (RT) domain, the RT validation of applications running on MPSoCs is indispensable to

3

guarantee their safe usage. Yet the timing analysis of MPSoC platforms with hard real-time requirements is very challenging making their usage in safetycritical real-time domains difficult. In difference to a single-processor platform an access to a shared resource in an MPSoC can have variable delays depending on the level of interleaving with other processors trying to access the same resource; e.g. if Task A on pe<sub>0</sub> and Task B on pe<sub>1</sub> simultaneously issue an access request on the shared bus, then depending on the arbitration mechanism either pe<sub>0</sub> or pe<sub>1</sub> could win the arbitration and is granted access causing the other processor to delay. In addition to resource sharing, the fact that in industrial MPSoCs' architectures, efficiency (or optimized average-case performance) is still preferred over predictability makes the real-time analysis of such systems even harder. A typical example is the abundant usage of shared caches (with complex replacement strategies) in current MPSoCs which obviously increases the average-case performance of a platform but makes it difficult to perform a RT analysis due to the unpredictable nature of caches (with complex replacement strategies see [Cullmann et al., 2010]). Thus, in a full-featured MPSoC, the contention (as seen in the previous examples) not only can take place at the level of communication resources (bus, interconnects) but also on the level of storage resources (shared memory, caches) which makes the RT analysis of such platforms very challenging.

Due to this fact, adapting traditional static RT analysis methods which are well-established for single-processor platforms for MPSoCs is not an easy task. This in turn, stresses the need for novel RT analysis methods capable of proving the timing predictability of realtime applications running on MPSoCs at an early project stage. cope with the above challenge, there is a lot of active research on designing predictable<sup>2</sup> MPSoCs [Chattopadhyay and Roychoudhury, 2011, Cullmann et al., 2010, Nelis et al., 2011, Hansson et al., 2009, Metzlaff et al., 2011, Ungerer et al., 2010, Wilhelm and Reineke, 2012, Zamorano and Juan, 2014] on one side (see Sect. 2.3.6) and enhancing the traditional static analysis methods to be able to predict execution times of embedded applications running on MPSoCs on the other side (see Chap. 3).

In [Cullmann et al., 2010], the authors suggested the design of timing predictable MPSoCs to overcome this challenge and gave receipts how to design MPSoCs for predictability. They suggested to support shared communication resources with easy-to-predict arbitration protocols and to use private storage resources (referred to as spacial isolation) to alleviate contention. For Commercial-Off-The-Shelf (COTS) multicore platforms a smart configuration can be done for making them predictable. This configuration discourages the

<sup>&</sup>lt;sup>2</sup>Predictable MPSoCs are those exhibiting deterministic temporal behavior enabling beforehand to determine whether or not the right outputs happen at the right (predicted) moment.

usage of shared caches in COTS, enables partitioning of memories (if supported by the hardware) to avoid interferences among the cores and utilizes predictable arbitration features of communication resources (as in the MPC8641D avionic processor in [Cullmann et al., 2010]).

An excerpt of first approaches enhancing traditional static analysis towards MPSoCs will be discussed in Chap. 3. There are mainly two real-time (RT) analysis approaches for embedded applications: dynamic and static (formal) methods. In the dynamic methods, use-case driven timing measurements of the application are performed either using a virtual-hardware platform simulation model (with variable abstraction levels ranging from untimed to cycle accurate) or by running it on the target hardware employing hardware tracing facilities. This approach is still state-of-the-art in industry since it is capable of handling systems with a huge state space. Yet it is not applicable to applications with hard real-time requirements since even exhaustive simulations provide no guarantee that all interesting corner cases are covered. According to DO-178B/DO-178C, dynamic testing-based real-time analysis methods alone are not enough since testing cannot show the absence of errors [Kästner Daniel and Christian, 2014]. In a static (formal) approach, mathematical analysis is performed on a formal representation of both software and hardware. This analysis takes into consideration all possible inputs (use-cases) and combinations of the running applications with all different hardware states of the proposed platform. This makes it possible to identify the worst-case path and to estimate a pessimistic but a safe upper bound on the application execution time. Formal methods guarantee complete coverage of the considered model<sup>3</sup> but suffer from state explosion and scalability issues on one side and of obtaining over-pessimistic timing results (depending on the accuracy of the formal model) on the other side.

As explained above, in order to give safe timing guarantees under all conditions, a formal approach is needed to calculate safe lower/upper bounds based on Worst-Case-Execution Times (WCETs) of the application computation and communication phases depending on the target hardware platform. Since current MPSoCs are composed of concurrent components and their synchronization depends on timing constraints, formal models like timed-automata and model-checkers like UPPAAL [Bengtsson and Yi, 2004] are very suitable to capture and verify their temporal behaviors with rigor. In addition, for unmet timing properties counter examples are provided. Another motivation for using state-based RT analysis methods for analyzing MPSoCs' applications in this thesis, is that they support modularity which makes them easily adaptable to different hardware models. Furthermore, state-based RT analysis methods pos-

<sup>&</sup>lt;sup>3</sup>Of course this does not imply that the considered model is complete (i.e. represents all relevant corner cases), but formal methods enable complete exploration, independent from the fact whether this model is complete or not.

sess the capability of getting more accurate results [Perathoner et al., 2009] and verifying more complex properties than other formal methods (see Sect. 3.1).

But one of the main drawbacks of recent research using state-based RT analysis methods for analyzing MPSoCs (see Sect. 3.1.2.1) is trying to analyze arbitrarily parallel programs at code-level on MPSoC architectures. Despite the advantage of such an approach being applicable to any code written/generated for any domain, yet the fine granularity of the code-level or instruction-level makes the state-based methods not scalable. In order to circumvent their scalability problem, enabling a composable state-based RT analysis is a prerequisite. This can only be done if we have a task model which exhibits clean semantics that enables distinguishing communication from computation parts in the implemented code which is not the case for generic tasks. With these aspects (communication from computation phases) separated, flexible mapping to different target platforms can be established, and a composable RT analysis method analyzing different mappings is possible.

In this thesis, we aim to develop a state-based RT analysis method to guarantee a timing predictable execution of parallel software on MPSoCs. Our state-based RT analysis method targets, on the one side, the analysis of larger systems (for a chosen use-case in Sect. 7.2.1 up to 96 actors mapped to 4-tiles and up to 320 actors on a 2-tiles platforms) than those analyzable by current state-based approaches and, on the other side, achieving a significant precision improvement (up to a percentage improvement of 300%) compared with a state-of-the-art analytical method. The establishment of our method, would open the way for safety-critical domains, especially in the most conservative domains such as avionics<sup>4</sup>, to adapt MPSoCs (for small-scale systems) in their design flow, making it easier to pass the strict certification processes imposed by certification authorities. Clearly, integrating multiple functionalities on a single MPSoC would lead to great saving in terms of the hardware used, making products cheaper and thus more competitive.

## 1.2 Research Questions and Contributions

### 1.2.1 Research Questions

As described above, the main concern of a system-level designer is to develop MPSoCs, benefiting from their performance and energy advantages compared to a single-processor platforms, and at the same time guaranteeing that the hard real-time requirements of the applications mapped to them are met. Now the main challenge here is to provide suitable methods to guarantee timing-predictable execution of parallel software on MPSoCs. One of these methods

<sup>&</sup>lt;sup>4</sup>Currently in the avionics single-core federated architectures are still used.

which we will be using in thesis to achieve this goal is the state-based RT analysis methods (see Sect. 2.5.2.1). As we already explained, for a state-based RT analysis method a formal model of the hardware and the application should be built. The question is now how to build a model of the real hardware/software being of a reasonable size (improving the scalability bottleneck of state-based RT methods with generic task models see Sect. 3.1.2.1) on one hand and of a reasonable granularity on the other hand allowing an accurate real-time analysis of the System Under Analysis (SUA).

To answer the above question, the following research subquestions must be answered:

- 1. Which constraints should be imposed on the software application in order to be modeled in an abstract but still accurate form?

- 2. Which constraints should be imposed on the physical platform and which timing properties shall be represented in the formal platform model?

- 3. How does the formal model scale w.r.t to state-space complexity? How does the approach perform in terms of correctness and accuracy (over-approximation evaluation)?

- 4. Which kind of properties can be obtained/validated via a state-based RT analysis approach? (end-to-end deadline, WCRT, buffers' sizes etc.)

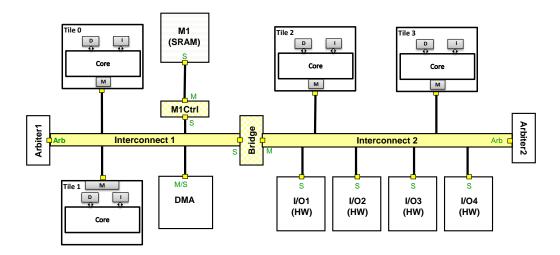

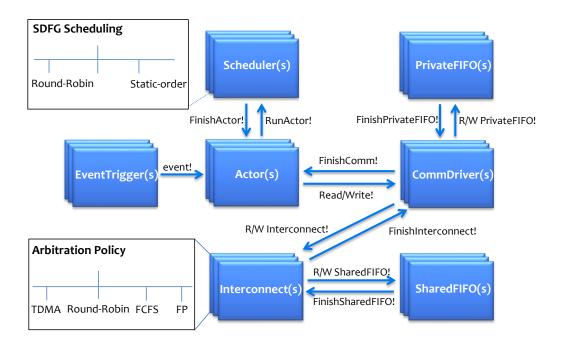

In order to answer the first question and to circumvent the scalability issues faced by previous state-based RT analysis approaches, we limit applications to the Synchronous Data-flow (SDF) [Lee and Messerschmitt, 1987b] Model of Computation (MoC) (see Chap. 4). In the context of MPSoCs research [Sriram and Bhattacharyya, 2000, Shabbir et al., 2010, Ghamarian, 2008, Kumar, 2009, Moonen, 2009, Stuijk, 2007], the SDF MoC is gaining consideration due to its analyzability features (e.g. deadlocks and bounded buffer properties are decidable for such models [Lee and Messerschmitt, 1987b]). In an SDF specification, parallelism is represented explicitly and static schedules can be obtained. Furthermore, SDF semantics support a clean separation between computation and communication since no communication (resource access) is allowed during the computation phase. This enables a compositional timing analysis where SDF actor execution times can be analyzed independently from communication delays of message passing between SDF actors.

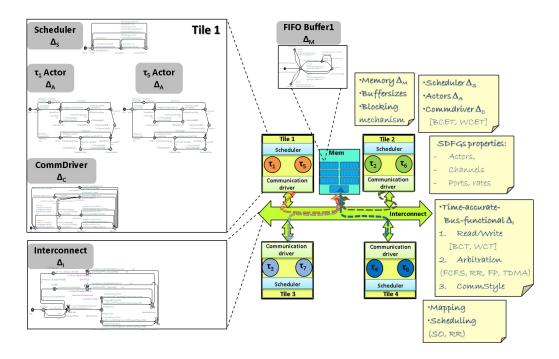

We also constrain our hardware platform to an MPSoC architecture (see Chap. 4) where each processor has its own instruction and data memory, called a "tile". Tiles are connected through one (or more) arbitrated shared interconnect(s) (bus(s), shared DMA(s)). Communication between tiles is realized through FIFO-style message passing on shared memories accessed via shared interconnects.

With these constraints a formal model based on timed-automata semantics can be constructed (see Chap. 5), representing WCETs of SDF actors and access protocol properties (including timing) of shared interconnects, private local and shared memories of the MPSoC platform and questions 3&4 can now be examined (see Chap. 7). With the above knowledge we can now concretely formulate the main research goal of this thesis as follows:

The main goal of this thesis is to examine (according to metrics defined in questions 3&4) a state-based real-time analysis approach to analyze multiple Synchronous Data-Flow (SDF) applications running on MPSoCs with shared communication resources with respect to their hard real-time requirements.

#### 1.2.2 Contributions

We claim the following contributions in this thesis:

- **C1** We provide a predictable, yet realistic, configuration of MPSoCs (with dynamic arbitration protocols) which enables our state-based RT-analysis method (see Chap. 4).

- **C2** We enable a state-based real-time analysis of multiple SDF applications mapped to an MPSoC platform (see Chap. 5):

- 1. Through capturing the delays of SDFGs when run on an MPSoC in the form of timed-automata (TA) templates enabling sensitivity to external events, multiple interconnects, multiple storage resources and different inter-processor communication styles. For this we provide the complete set of timed automata templates capturing the considered system model performance metrics and explaining their implementation and abstraction decisions,

- 2. Evaluating different methods to improve the scalability of our state-based RT analysis method,

- 3. Allowing the verification of more complex properties (such as liveness and reachability properties) compared to other analytical methods.

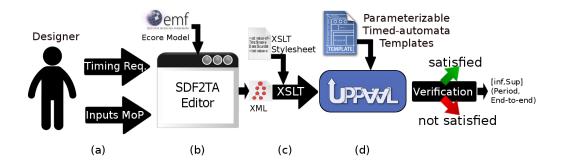

- C3 Integrating above state-based RT analysis method into a model-based design-flow which enables functional and temporal analysis of control applications at different abstraction levels (see Chap. 6):

- 1. Translation concept of Simulink models to SDFGs enabling RT analysis of applications implemented in Simulink (implemented by Warsitz in SimulinkToSDF tool [Warsitz, 2015, Warsitz and Fakih, 2016]),

- 2. Automation concept of our state-based RT analysis (first implemented by Schlaak in SDF2TA tool [Schlaak, 2014]),

- 3. Combining a simulative method<sup>5</sup> with our state-based RT method for functional and accurate temporal Verification and Validation (V&V).

### C4 Evaluating the viability of our approach (see Chap. 7):

- Being applicable to industrial use-cases. For this we show that the timing bounds of different implementations with different communication styles for a motor control use-case are predictable through our framework,

- 2. Tightening real-time results in comparison to a pessimistic analytical approach from literature [Shabbir et al., 2010],

- 3. Enabling analysis of larger systems compared to related work [Gustavsson et al., 2010, Lv et al., 2010].

In this thesis, our major contribution is the development of a state-based real-time analysis framework (see C2) which enables (using the UPPAAL model-checker) calculating safe timing bounds of multiple (hard real-time) SDF-based applications running on an (for predictability pre-configured see C1) MPSoC (represented as a network of TA), considering variable access delays due to the contention on shared communication resources. The analysis framework is capable of handling different shared memory architectures, data access granularities and arbitration protocols (such as Round Robin, Fixed Priority and First Come First Serve (FCFS)).

To the best of our knowledge, we pioneered the translation of SDFGs to timed-automata (in [Fakih et al., 2013a]) and we were the first to describe how to use model-checking to analyze real-time properties (e.g. end-to-end deadline) of hard real-time multiple SDF applications mapped to MPSoCs. Our approach has been later taken up by other researchers in [Malik and Gregg, 2013, Ahmad et al., 2014, Zhu et al., 2014, Zhu et al., 2015, Skelin et al., 2015, Thakur and Srikant, 2015] in order to model-check SD-FGs/SADGs<sup>6</sup>, targeting various objectives (see Sect. 3.1.2.2).

Another major contribution is that we integrated our developed RT method in a model-based design flow (see C3) simplifying the design of MPSoCs applications and their validation. Here, we support Simulink models as entry

<sup>&</sup>lt;sup>5</sup>The Virtual-Platform-In-the-Loop (VPIL) verification and validation technique was first demonstrated for single-processor platforms in [Fakih et al., 2011, Fakih, 2011] and in the scope of this thesis it was then extended for Verification and Validation (V&V) of MPSoCs and published in [Fakih and Grüttner, 2012].

<sup>&</sup>lt;sup>6</sup>Scenario-aware Data-flow Graphs (SADGs) are more dynamic SDFGs where according to scenarios, different flavors of the same SDFG are executed.

9

models and describe how such models can be translated to SDFGs to enable their state-based RT analysis on the one side. On the other side, we introduce a simulation-based RT analysis (VPIL see C3-3) in the design flow enabling functional and temporal validation of embedded Simulink applications on MP-SoCs. Simulative approaches are more accurate and can be applied to analyze large-scale applications running on large MPSoCs (for e.g. in the case where the state-based RT analysis fails to analyze the SUA due to the well-known state-space explosion problem).

### 1.3 Thesis Outline

This thesis is structured as follows. In Chap. 2 we will first discuss the main concepts relevant to this thesis. Afterwards we will briefly discuss the related work in Chap. 3 mainly addressing the RT analysis of SDFGs on MPSoCs. The core of this thesis lies in chapters 4, 5 and 6 where we first introduce and discuss the constraints made on the application and hardware model to enable the applicability of our state-based RT analysis method. Then we illustrate our proposed approach and elaborate on the implementation of our timed-automata templates used to capture the system model. Afterwards, we describe our overall model-based design flow. Chap. 7 presents the experimental evaluation conducted to demonstrate the viability of our state-based RT method. Finally, Chap. 8 summarizes our findings and gives an outlook on open issues and future work.

### 1.4 Prior Publications

Most of the concepts illustrated in this thesis have been published beforehand in scientific journals, conferences, and workshops by the author (as first author) together with other researchers which contributed mostly through their thoughts in discussions, guidance and feedback to the written publications.

A first proposal answering the four questions (see Sect. 1.2) was published in [Fakih et al., 2013a]. A scalability improvement in terms of the number of applications being analyzable of our approach through enabling spatial and temporal segregation in the MPSoC was published in [Fakih et al., 2013b].

The Virtual-Platform-In-the-Loop (VPIL) verification and validation technique was first demonstrated for single-processor platforms in [Fakih, 2011, Fakih et al., 2011] and in the scope of this thesis it was then extended for V&V of MPSoCs (see Sect. 6.4) and published in [Fakih and Grüttner, 2012].

In [Fakih et al., 2014] our simulative approach (VPIL technique) was combined with our state-based RT analysis approach in a model-based design flow

and the applicability of our approach was demonstrated on an industrial usecase.

In [Fakih et al., 2015] the restrictions made in the previous publications were further relaxed towards enabling sensitivity to external events, multiple interconnects, multiple storage resources and different inter-processor communication styles. In addition, we published in [Fakih et al., 2015] the complete set of used timed automata templates capturing the considered system model performance metrics and explaining their implementation and abstractions' decisions.

It is important to note that the first version of the SDF2TA tool (see Sect. 6.3) enabling the automatic configuration of our timed-automata templates was implemented by Schlaak [Schlaak, 2014]. Also the first version of Simulink-ToSDF tool which enables translating Simulink models to SDFGs was first developed by Warsitz in [Warsitz, 2015] (based on a major conceptual contribution by the author of this thesis summarized in Sect. 6.2) and then published in [Warsitz and Fakih, 2016]. Both scientific work above were performed under the guidance and support of the author of this thesis.

## Chapter 2

# **Basic Concepts and Background**

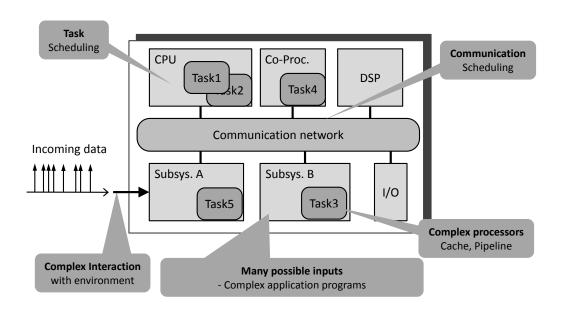

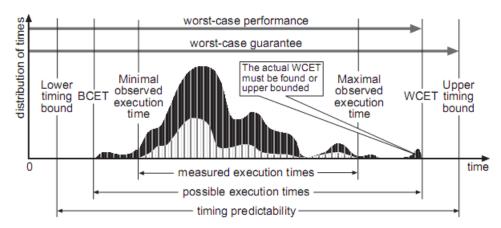

Figure 2.1: Timing issues of MPSoCs' embedded applications (taken from [Roychoudhury, 2009])

This chapter explains the basic terms important for understanding further work in this thesis. Definitions of basic keywords can be found in the glossary (see Glossary B.2.2). Fig. 2.1 shows an overview of different issues which should be taken into consideration when validating the timing properties of embedded applications running on MPSoCs. These factors vary between the influences of the different timing patterns of incoming events (periodic, sporadic, with/without jitter) from the external environment which activate the local tasks, the task model semantics and task scheduling, the application possible

input behavior and the communication access pattern on the communication resources. In addition, the hardware properties of MPSoCs largely influence the timing behavior of the application including the complexity of processors (including cache, pipelines) and the temporal properties of the communication (latency, arbitration complexity) and storage resources.

This chapter will be structured according to these issues depicted in Fig. 2.1. Starting with a short description of current system-level design methodologies, we will then take a look at the task models (with a focus on the synchronous data-flow graphs) considered in this thesis and their scheduling mechanisms in Sect. 2.2.1. Next, the temporal behavior of different MPSoC components with a focus on the communication resources (arbitration policies and timing diagrams) temporal behavior is described in Sect. 2.3. Afterwards, a short description of modeling the interaction with the environment and its timing effect is given. At the end of this chapter, we will take a look at different real-time (RT) timing analysis methods with the focus on formal RT analysis methods, being able of handling the timing issues in Fig. 2.1.

### 2.1 System Level Design (SLD) Methodologies

One goal of this thesis (see C3) is to implement a suitable design flow to enable timing validation of functional models (see Chap. 6), that is why some concepts and terms of the SLD methodologies are presented in the following (partially taken from the author's work in [Fakih, 2011]).

Basically SLD methodologies aim at introducing "abstraction" as a solution for handling the design complexity of embedded systems. In the 1960s capture and describe methodology was used [Gajski et al., 2009]. Software and hardware design were separated by a gap because developers had to wait until gate level design was finished before verifying the system specifications. After that designers began to use the describe and synthesize methodology where designers first specified what they wanted in boolean equations or Finite State Machines (FSM) descriptions and synthesis tools were implemented to generate automatically implementations of these descriptions in the form of netlists. But still there was a great gap between higher system level and these low-level specifications. Nowadays the specify and explore methodology is the method used to close this gap, the level of abstraction is increased beginning with a functional model implemented in some Model of Computation (MoC) representing an executable specification, then possibilities are explored at different refinement levels before finally the model is refined to be implemented on the target hardware.

In [Gajski et al., 2009], MoCs are defined as follows:

"A Model of Computation (MoC) is a generalized way of describing

system behavior in an abstract, conceptual form." [...] MoCs are generally based on a decomposition of behavior into pieces and their relationships in the form of well-defined objects and composition rules." ([Gajski et al., 2009]:50)

MoCs can be classified into process-based and state-based models. Processbased models are typically used for data-oriented applications and for design modeling at behavioral level. They are represented by a set of concurrent processes, that are untimed and ordering is only limited by the data flow between them. Each process is blocked when trying to read from a channel with insufficient data and it resumes when enough data is available. In a data-flow model, which is a special case of process-based models, processes are replaced by atomic blocks of execution, called actors. Avoiding the need for context switches in the middle of processes, actors execute according to firing rules depending on the number of tokens that must be available on every input for the actor to fire [Gajski et al., 2009]. Synchronous data-flow (SDF) MoC [Lee and Messerschmitt, 1987a] is a data-flow model, in which the number of tokens consumed and produced by an actor per firing is constant and fixed (see Sect. 2.2.1). State-based models on the other hand, focus on explicitly exposing and representing control flow. They are used for controldominated applications and for modeling of designs at the implementation level (e.g. for capturing cycle-by-cycle hardware behavior). Process State Machines (PSM) combines both process-based and state-based concepts in a one MoC [Gajski et al., 2009]. As an instance SystemC the well-known standard modeling language [IEEE-1666, 2012] for realizing virtual-hardware-platforms has a generic MoC which only assumes that the system state changes at discrete time points. This means that for example both a PSM [Gerstlauer, 2009] or a Timed Data-Flow (TDF) [Grimm et al., 2009] MoCs can be realized in SystemC.

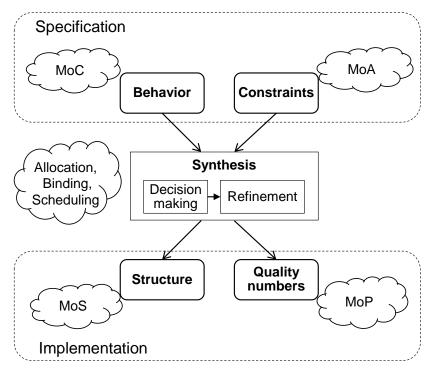

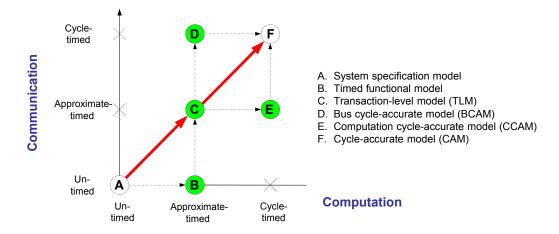

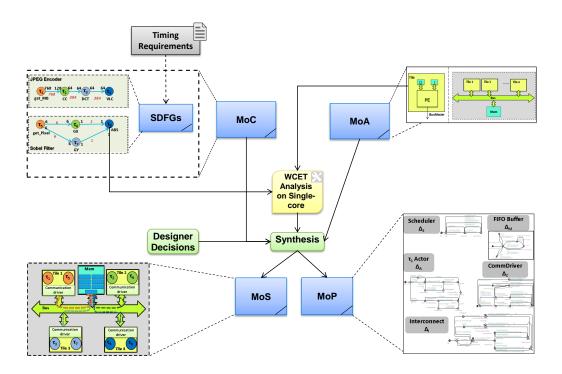

Fig. 2.2 shows the X-chart [Gerstlauer et al., 2009] which identifies the main tasks in modern Electronic System Level (ESL) design process. All the definitions and terms of the system model used in this thesis (see Chap. 4) are based on the X-Chart defined and described in [Gerstlauer et al., 2009]. The functionality of the system is first captured in a behavioral model which typically represents an executable specification of the system functionality. The expressibility and analyzability of the behavioral model depends on its underlying Model of Computation (MoC). In this thesis, we will mainly use the SDF MoC (see Sect. 2.2.1). Later on, Simulink (see Sect. 2.2.2) will also be supported in our design flow to capture behavioral made. The Model of Architecture (MoA) (see Fig. 2.2) represents a platform model where the architectural template, decisions and constraints are taken into consideration for e.g., available resources, their capabilities and their interconnections [Gerstlauer et al., 2009].

Figure 2.2: X-Chart (taken from [Gerstlauer et al., 2009])

The synthesis step includes the processes of allocating resources, binding and scheduling the behavioral model on the defined architecture, and thus transforming a specification into an implementation. An implementation consists of a structural model and quality numbers (in this thesis only timing delays quality numbers are considered). The structural model (MoS: Model of Structure) is a refined model resulting from the behavioral model under the architectural constraints given in the specification after the synthesis decisions above have taken place [Gerstlauer et al., 2009]. Different implementations parameters (for e.g. throughput, response time, latency, area and power) can be estimated for a specific implementation. Instead of implementing each design possibility to obtain above parameters' values, performance models (MoP: Model of Performance) are used. A MoP comprises all individual elements of the MoS contributing to a specific design quality (e.g. worst/average/best case latency). The overall quality estimates can be obtained either through direct measurements, through simulation or through static analysis and highly depends on the abstraction level and granularities in the MoP [Gerstlauer et al., 2009]. In this thesis, the performance values considered in the MoP are merely execution times metrics.

### 2.2 Task Model (Model of Computation)

Model-based Design (MBD) of embedded systems is nowadays, a standard, easy and efficient way for capturing and verifying embedded software functional requirements. The main idea is to move away from manual coding, and with the help of mathematical models create executable specifications, and then provide automatic code generators which generate consistent imperative code ready to be deployed in real environments. Typically, in MBD abstractions from non-functional issues are made for allowing much faster simulation speeds than other models enriched with hardware issues (e.g. Register Transfer Level (RTL) models). Although this allows the designer to validate requirements at very rapid speed, yet important issues such as timing violations of a safety critical embedded application can't be validated at this abstraction level.

In this thesis, we will mainly use the SDF MoC (see Sect. 2.2.1). Later on, our proposed design flow (see Sect. 6.1) will be extended to enable entry functional models modeled in Matlab/Simulink [MathWorks, Inc., 2015c] (see Sect. 2.2.2).

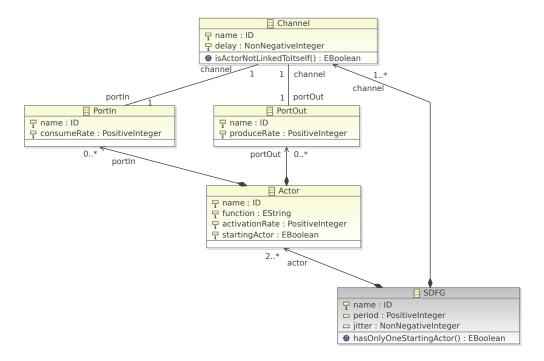

### 2.2.1 Synchronous Data-flow Graphs (SDFGs)

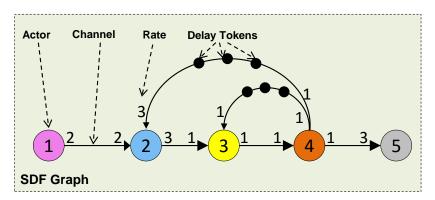

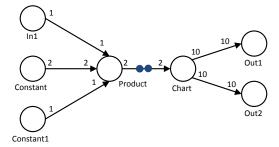

A synchronous (or static) data-flow graph (SDFG) [Lee and Messerschmitt, 1987b] is a directed graph (see Fig. 2.3) which, similar to general data-flow graphs (DFGs), consists mainly of nodes (called actors) modeling atomic functions/computations and arcs modeling the data flow (called channels). In difference to DFGs, SDFGs consume/produce a static number of data samples (tokens) each time an actor executes (fires). An SDFG suits well for modeling multi-rate streaming applications and DSP algorithms and also allows static scheduling and easy parallelization. An application which is modeled as an SDFG and has a timing requirement will be denoted as a synchronous (or static) data-flow application (SDFA) in this thesis. A port rate denotes the number of tokens produced or consumed in every activation of an actor. The data flow across a chan-

Figure 2.3: Example of an SDFG (based on [Lin et al., 2011])

nel (which represents a FIFO buffer) is done according to a First-In-First-Out (FIFO) fashion. Channels could also store initial tokens (called delays indicated by bullets in the edges see for e.g. Fig. 2.3) in their initial state which help resolving cyclic dependencies (see [Lee and Messerschmitt, 1987b]). An actor in an SDFG can be a consumer (*sink*), a producer (*source*) or a transporter actor. The complete formal definitions of SDFGs will be presented in Sect. 4.2.1.

Synchronous data-flow graphs where the number of tokens which are consumed or produced by all actors when activated, is always equal to 1 are called homogeneous synchronous data-flow graph [Lee and Messerschmitt, 1987a]. Below we will give a description of the basic concepts of SDFGs relevant to this thesis including their scheduling decisions, their analyzability (properties of SDF graphs that are analyzable) and expressiveness features compared to more dynamic data-flow models and the clustering technique which will be applied in Sect. 5.4.2.

### 2.2.1.1 Scheduling

Thanks to the a priori defined rates, a static periodic schedule (at compile time) for connected SDFGs can be easily constructed. Given an SDF specification, a schedule can be constructed by solving a topology matrix representing the SDFG [Lee and Messerschmitt, 1987a]. The number of columns in this matrix is equal to the number of actors. The entries to the matrix are either the number of produced tokens (positive number) or consumed tokens (negative). The SDFG in Fig. 2.3 can be described by following topology matrix:

$$T = \begin{pmatrix} 2 & -2 & 0 & 0 & 0 \\ 0 & 3 & -1 & 0 & 0 \\ 0 & -3 & 0 & 1 & 0 \\ 0 & 0 & 1 & -1 & 0 \\ 0 & 0 & -1 & 1 & 0 \\ 0 & 0 & 0 & 1 & -3 \end{pmatrix}$$

A Periodic Admissible Sequential Schedule (PASS) exists if the rank of the matrix rank(T) = s - 1 where s is the number of actors in the graph (c.f. proof in [Lee and Messerschmitt, 1987a]). A topology matrix has a proper rank (rank(T) = s - 1) if there is a strictly positive integer vector  $\gamma$  in its right nullspace (according to [Lee and Messerschmitt, 1987b]), meaning that  $T\gamma$  is the zero vector:

$$T\gamma = 0$$

where  $\gamma$  is called *repetition vector* and it describes the minimum number of activation of every actor in each scheduling period. An SDFG is said to be *consistent* (see Def. 4.2.4) if and only if a positive integer repetition vector  $\gamma$

exists. The schedule should be *periodic* because the the SDFG is assumed to a have an infinite stream of input data, *admissible* meaning that all actors are run only when data is available, and *sequential* meaning that the actors are executed sequentially on a single-processor [Lee and Messerschmitt, 1987b].

In our example in Fig. 2.3, the topology matrix T has a rank of 4 which is fulfills the condition that rank(T) = s - 1 (where s = 5) which implies that a valid PASS schedule exists.

$$\gamma = J \begin{pmatrix} 1 \\ 1 \\ 3 \\ 3 \\ 1 \end{pmatrix}$$

for any positive integer *J*.

Clearly if a schedule for a single processor (PASS) exists, then there also exists a schedule for multiple processors (PAPS), since in the trivial case all computation can be scheduled on the same processor [Lee and Messerschmitt, 1987a]. Heuristics which help constructing PAPS schedules can be found in [Lee and Messerschmitt, 1987a]. Describing these heuristics would be out of the scope of this work, since we assume an a priori constructed schedule for our real-time analysis method (see Sect. 4.1.1 in Chap. 4).

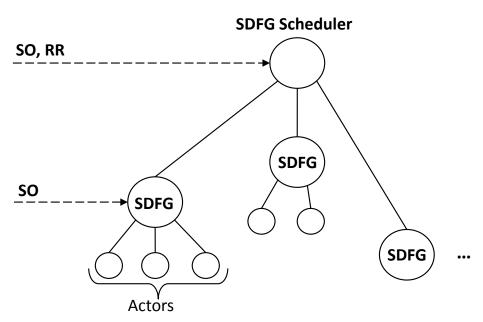

After describing the basic mathematical method to determine a PASS schedule, we now elaborate on the different existing scheduling methods (suggested in [Stuijk, 2007]) which can be used to realize scheduling of actors within the same SDF application on one side and scheduling between different SDF applications mapped to the same processor on the other side. These scheduling strategies are typically either *compile-time* scheduling (e.g. static-order scheduling) or *run-time* (e.g. round-robin and time division multiplex) strategies [Moonen, 2009]. In general, run-time scheduling requires a run-time supervisor (an operating system) which can lead to severe overheads in terms of performance. On the other hand, this is not the case for compile-time scheduling where (if any) only small run-time overheads are introduced due to the scheduling process (no need for an operating system).

In the following a short description of the scheduling mechanisms used in this thesis. In addition, we will take a look at each scheduling strategy, similar to [Stuijk, 2007], to see whether it is *composable* or *flexible*. According to [Stuijk, 2007], a scheduling strategy is said to be composable if the timing behavior of applications can be analyzed in isolation. Flexibility of a strategy is defined, by the ability to deal with dynamically changing dependencies between actors [Stuijk, 2007].

Static-order Scheduling A static-order schedule for a set of actors (potentially of different SDFGs) where these actors are executed in a cyclic manner according to statically ordered list, as soon as their input data is available [Stuijk, 2007]. This means that a scheduler will wait until the first actor in the list gets ready (as soon as all its input data are available), then executes the ready actor and move to the next actor in the list ready to be executed. Clearly, a static-order scheduling is neither flexible nor composable. It is not flexible since all dependencies between the actors must be fixed and known at compile time [Stuijk, 2007]. The non-composability of static-order schedules is obvious since no actor or set of actors within such a schedule can be analyzed in isolation, as the inter-actor dependencies must be always taken into consideration.

Round-Robin Scheduling Round-robin (RR) scheduler can help to achieve more fairness to the execution of ready actors than the static-order schedule. Similar to the static-order scheduler, it gets a list of ordered actors, but with the difference that the RR scheduler checks if the current actor is ready (for e.g. check for input availability or output capability) then it either fires or gives the control back to the scheduler if this is not the case. In both cases of blocking or successful firing, the scheduler switches from the active actor to activate the next actor in the list. In addition to fairness, RR scheduling gives the required flexibility to handle actors for which the order of execution are not known when constructing the schedule [Stuijk, 2007].

Since every actor should wait for all actors to run in the list before it gets to run in the worst case, the worst-case response time of an actor in RR schedule can be calculated as follows:

$$t_{wcrt_j} = \sum_{\forall i \neq j} t_{wcrt_i} \tag{2.1}$$

RR scheduling is not composable since the response time of an actor strongly depends on the execution time of all actors in the schedule [Stuijk, 2007].

**Time-Division Multiple-Access (TDMA) Scheduling** A TDMA scheduler allows an actor to be executed in only specific time slot and switches to the next slot as soon as the previous slot expires, using the concept of periodically rotating wheel [Stuijk, 2007].

Since we consider, in this thesis, a non-preemptive (for the preemptive one c.f. [Stuijk, 2007]) TDMA scheduler (as assumed also in [Giannopoulou et al., 2012]), we assume that the worst-case execution time of an actor (or cluster of actors, details on this will follow in Sect. 5.4.3) does not

exceed the size of the corresponding slot. The following equation can now be used to calculate the worst-case response time of an actor in TDMA schedule:

$$t_{wcrt} = \sum_{i=0}^{Sl} T_i + (Sl \times \mathbf{s}), \tag{2.2}$$

where  $T_i$  is the slot size (in time units) of current slot i, s is the scheduler worst-case delay time needed to switch from one slot to another and Sl is the total number of slots.

It is obvious from Eq. 2.2 that the TDMA scheduling mechanism is composable, due to the fact that the worst-case response time of every actor can be analyzed in isolation from others since it is only affected by the slot length and the number of slots. Moreover, the TDMA scheduling is flexible in the sense that new actors can be added to the TDMA schedule as long as there are unreserved slots available [Stuijk, 2007].

A comparison was made between the above three scheduling methods in [Stuijk, 2007]. The author came to the conclusion that even though the TDMA scheduling is flexible and supports composability, it can (potentially) lead to over-allocation of resources in order to compensate the timing overheads for e.g. in the case where large portions of the slots are unoccupied.

In this work, we assume (see Sect. 4.1) that all scheduling strategies are non-preemptive meaning that actors cannot be preempted by the scheduler and they have to actively hand the control back to the scheduler after finishing or when blocking. While non-preemptive schedulers are easy to implement and overheads of scheduling are easily assessable, yet the non-preemptive scheduling is known to be NP-hard even for single-processor platforms [Jeffay et al., 1991].

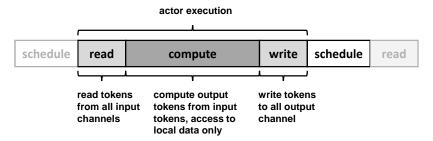

The above mentioned worst-case response time of actor  $(t_{wcrt_i})$  is defined in this thesis as follows:

$$t_{wcrt} = t_{wcet} + t_{com} + t_{wait} (2.3)$$

where  $t_{wcet}$  is the worst-case execution time of the actor when run on a single target processor (which can be achieved through a static analyzer see Sect. 2.5),  $t_{com}$  is the communication time needed by every actor firing to transport a number of tokens over a communication resource and  $t_{wait}$  is the waiting time of the actor induced when waiting for other actors to finish communication on communication resources.

#### 2.2.1.2 Timing Properties

When mapped to an MPSoC, SDFGs exhibit interesting timing properties as shown in the example in Fig. 2.4. In this example we have an SDFG of five

<sup>&</sup>lt;sup>1</sup>Deciding schedulability for a set of concrete periodic tasks is NP-hard in the strong sense [Jeffay et al., 1991].

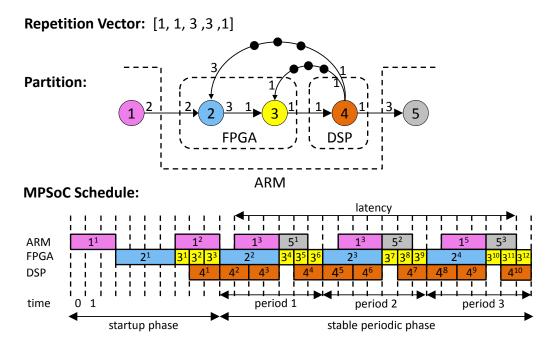

actors and an MPSoC of three heterogeneous processors: one ARM processor, one Field Programmable Gate Array (FPGA) and one Digital Signal Processor (DSP). The next step would be to obtain a valid periodic static-order schedule (see Sect. 2.2.1.1) represented by the repetition vector as seen in Fig. 2.4 where except actors 3 and 4 (which should be executed three times) all other actors should be executed once. Then, the SDFG is partitioned in three partitions with the first partition consisting of actor 1 and actor 5 which are mapped to the ARM processor, the second partition consisting of actor 2 and actor 3 which are mapped to the FPGA, and the third partition consisting of actor 4 which is mapped to the DSP. These mappings could be reasonable depending on the nature of the actors and which criteria the designer wants to optimize (for e.g. energy, performance or cost purposes).

After being mapped to the MPSoC, actors are run according to the periodic static-order schedule (based on repetition vector in Fig. 2.4) on every processor and their resulting MPSoC schedule is shown in Fig. 2.4. As we can observe the SDF application goes through a *startup phase* (which could comprise several *iterations*) before it reaches the *stable periodic phase*. An iteration is a set of actor firings such that each actor in the SDFG has the same firing number as calculated in the repetition vector [Stuijk, 2007] . If we take a look at our example, then the SDFG needs a *period* of 7 units of time to complete a single iteration

Figure 2.4: Example of an SDFG with its relevant timing properties (taken from [Lin et al., 2011])

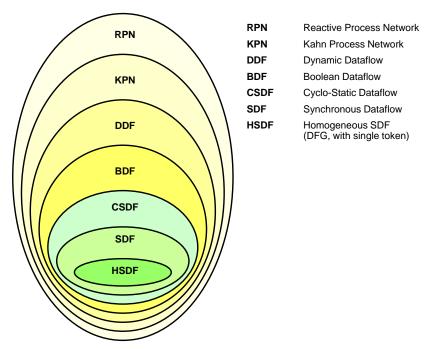

Figure 2.5: Process-based MoCs (taken from [Basten, 2008]), MoCs from BDF and above (highlighted with yellow) are Turing-complete

in the stable periodic phase (thus if one unit of time is equal to one cycle, then every 7 cycles an iteration of the SDFG is completed). For processors having 300 MHz clock frequency, we can reach a maximal *throughput* of about 43 MHz or about 43 Million iterations per second. Another relevant timing metric is the *latency* which is defined as the time duration from the first instance of the source actor of an SDFG to the last instance of the sink actor. In our example the latency is found to be equal to 19 units of time. In this thesis, we will only consider lower and upper bounds of the timing metrics (such as the worst-case period). By doing this, average timing estimations (such as average application throughput estimation) are no longer possible. The formal definitions of relevant properties (period, end-to-end latency, etc.) of SDFGs which are used in thesis are found in Sect. 5.2.8 and Sect. 4.2.1.

### 2.2.1.3 Expressiveness

According to [Moonen, 2009] homogeneous SDFGs and SDFGs have the same expressiveness as marked graphs [Commoner et al., 1971] and weighted marked graphs, which are a sub-class of timed petri-net theory, respectively. Despite the analyzability advantage of SDFGs (e.g. deadlocks and bounded buffer properties are decidable for such models [Lee and Messerschmitt, 1987b] and with the help of mathematical methods easy-to-analyze compile-time

schedules can be constructed), yet this comes at the cost of expressiveness.

One of the main limitations of SDF MoC is that dynamism cannot be handled for e.g. in the case where depending on the current scenario the application rates changes (this dynamism can be handled by an extension of SDFGs: the so-called Scenario-Aware Data-Flow (SADF) [Theelen et al., 2006] MoC). The fact that SDFGs do not support dynamism, makes SDFGs not adequate for many use-cases. Some of these were stated in [Schaumont, 2013], for e.g. stopping and restarting an SDFG is not possible since an SDFG can have only two states either running or waiting for input. In addition, reconfiguration of an SDFG to be able to (de)activate different parts depending on specific modes is not possible. Moreover, different rates depending on run-time conditions is not supported. Also modeling exceptions which might require deactivating some parts of the graph is not possible.

Another limitation (c.f. [Lee and Messerschmitt, 1987a]) of the SDF MoC is that conditional control flow is only allowed within an actor functionality but not among the actors. However, emulating control flow within the SDFG is possible even though not always efficient (c.f. [Schaumont, 2013]). An additional issue is that the SDF model does not reflect the real-time nature of the connections to the real-time environment.

More expressive data-flow graphs are shown in Fig. 2.5. A short description of these data-flow graphs can be found in [Kumar, 2009, Stuijk, 2007]. It is worth to note that the Boolean Data-flow graph (BDF) MoC which only extends the SDF MoC by enabling conditional and data-dependent execution (by adding *select* and *switch* control actors with boolean control inputs) is Turing-complete (c.f. [Buck, 1993]).

### 2.2.1.4 Clustering Methods

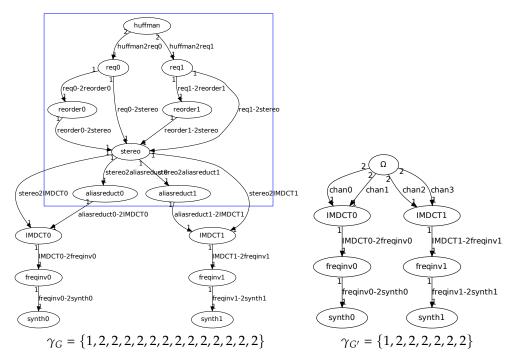

Multiple actors of an SDFG can be merged (clustered) together into one actor for various optimization purposes. In the following, the formal notation of the clustering method taken from [Bhattacharyya et al., 1997] (which we will use in Sect. 5.4.2) is presented.

Given a connected, consistent (see Def. 4.2.4) SDF graph  $G = (\mathcal{A}, \mathcal{D})$  (where  $\mathcal{A}$  is the number of actors and  $\mathcal{D}$  is the number of channels with a repetition vector  $\gamma_G$ , a subset  $\mathcal{Z} \subseteq \mathcal{A}$ , and an actor  $\Omega \notin \mathcal{A}$ . Clustering  $\mathcal{Z}$  into  $\Omega$  means generating the new SDFG  $(\mathcal{A}', \mathcal{D}')$  such that:  $\mathcal{A}' = \mathcal{A} - \mathcal{Z} + \{\Omega\}$  and  $\mathcal{D}' = \mathcal{D} - (\{e \mid (src(e) \in \mathcal{Z})\}) + \mathcal{D}^*$ , where  $\mathcal{D}^*$  is a "modification" of the set of edges that connect actors in  $\mathcal{Z}$  to actors outside of  $\mathcal{Z}$ .

For each  $e \in \mathcal{D}$  such that  $src(e) \in \mathcal{Z}$  and  $dst(e) \notin \mathcal{Z}$ , we define e' by:

$$src(e') = \Omega, dst(e') = dst(e),$$

$delay(e') = delay(e), cons(e') = cons(e),$

$prod(e') = prod(e) \times (\gamma_G(src(e))/\rho_G(\mathcal{Z}))$

where  $\rho_G(\mathcal{Z}) = gcd(\{\gamma_G(A) \mid A \in \mathcal{Z}\})$ , prod(e) and cons(e) are production and consumption rates of edge e receptively. Similarly, for each  $e \in \mathcal{D}$  such that  $dst(e) \in \mathcal{Z}$  and  $src(e) \notin \mathcal{Z}$ , we define e' by:

$$src(e') = src(e), dst(e') = \Omega$$

$delay(e') = delay(e), prod(e') = prod(e),$

$cons(e') = cons(e) \times (\gamma_G(dst(e))/\rho_G(\mathcal{Z}))$

and then, we can specify  $\mathcal{D}^*$  by:

$$\mathcal{D}^* = \{ e'(src(e) \in \mathcal{Z} \text{ and } dst(e) \notin \mathcal{Z}) \text{ or }$$

$$(dst(e) \in \mathcal{Z} \text{ and } src(e) \notin \mathcal{Z}) \}$$

The graph that results from clustering  $\mathcal{Z}$  into  $\Omega$  in G is denoted  $cluster_G(\mathcal{Z},\Omega)$ .  $\mathcal{Z}$  is clusterable if  $cluster_G(\mathcal{Z},\Omega)$  is consistent and G is acyclic. If  $G=(\mathcal{A},\mathcal{D})$  is a connected, consistent SDF graph,  $\mathcal{Z}\subseteq\mathcal{A}$ , and  $G'=cluster_G(\mathcal{Z},\Omega)$ , then  $\gamma_{G'}(\Omega)=\rho_G(\mathcal{Z})$ , and for each  $A\in(\mathcal{A}-\mathcal{Z})$ ,  $\gamma_{G'}(A)=\gamma_G(A)$ .

Fig. 2.6 shows an example of clustering an MP3 decoder application<sup>2</sup> according to the above clustering technique, which we will evaluate later (see Sect. 7.2.4) to show the possible improvements of our state-based RT method when utilizing the clustering mechanism.

### 2.2.2 Simulink

In the following, a short summary (partially taken from the author's work in [Fakih, 2011]) about Matlab/Simulink main features (including the simulation kernel and the code-generation features) and its MoC is given. Simulink is a software package for modeling of *dynamic systems* and simulating them in virtual time. Modeling of such systems is carried out graphically through Simulink graphical editor consisting mainly of blocks and arrows (*connections*) between them representing signals. Each block has its input, output and optionally state variables. The relationship of the inputs with the old state variables and the outputs update is realized through mathematical functions. Blocks could be linear or nonlinear, discrete or continuous. Discrete blocks are basically either logical *boolean equations* or blocks triggered through events,

<sup>&</sup>lt;sup>2</sup>MP3 decoder original definitions and timings were taken from [Stuijk et al., 2006]

Figure 2.6: MP3 decoder clustering:  $cluster_G(\{huffman, req0, req1, reorder0, reorder1, stereo, aliasreduct0, aliasreduct1\}, \Omega)$  with  $D^* = \{chan0, chan1, chan2, chan3\}$

while continuous blocks are expressed as differential equations. One of the powerful features of Simulink is the ability to combine multiple simulation domains (continuous and discrete). This is very useful for embedded systems, where in general the controller has discrete model and the environment often needs to be modeled as a continuous one. Simulink also supports a state-based MoC the *Stateflow* [MathWorks, Inc., 2015f] which is widely used to model discrete controllers. Simulink allows a fast *Model-in-the-Loop* (*MIL*) verification, where the functional model (of the controller for example) is simulated and results are documented to be compared with further refinements.

*Model of Computation* Since Simulink is our basic framework for capturing the functional model of the system in our design flow, it is relevant to know the underlying MoC. Authors in [Gajski et al., 2009] make the following statement:

"Dataflow models map well onto concepts of block diagrams with continuous streaming of data from inputs to outputs. As a result, they are widely used in the signal processing domain and as the basis for many commercial tools such as LabView [96] and Simulink [95]." ([Gajski et al., 2009]: 55)

This means that Simulink supports a data-flow MoC also referred to as the synchronous block diagram (SBD) in [Pouzet and Raymond, 2009]. In [Lublinerman and Tripakis, 2008] a method was presented to automatically transform SDFGs into SBDs, such that the semantics of SDF are preserved, and it was proven that Simulink can be used to capture and simulate SDF models. As a conclusion from the researches above, we can say that Simulink supports a timed data-flow MoC<sup>3</sup> which could be used to capture SDFGs.

Simulink also offers a control-based MoC represented in the *Stateflow tool-box*. The *Stateflow* language is based on the *statecharts formalism* supporting a combination of *Statecharts*, *Flowcharts* and *Truth tables*. The graphical *Statecharts* language directly realizes a *Hierarchical Concurrent Finite State Machine* (*HCFSM*) model as stated in [Gajski et al., 2009]. This means that a *Stateflow* diagram extends the classical finite state machine (pure Mealy or Moore automaton semantics) formalism by adding hierarchy and concurrency (parallel states). In this work, the *Stateflow* is only considered at the block level, thus abstracting from the single transitions and activities within this block.

Simulation Kernel Simulink uses an idealized timing model for block execution and communication, with both consuming no simulation time or in other words running infinitely fast. Typically, blocks are evaluated at certain time steps depending on a custom *fixed-step size* (or *sample time*) parameter, which can be set globally or individually for each block. This sample time parameter specifies the period of execution [Lee and Neuendorffer, 2005] of the model (or for each block). As mentioned before, Simulink supports both discrete time and continuous time simulation where the simulation of continuous models is based on differential equations. The values are interpolated using *numerical integration* techniques between the different time points of the fundamental sample time. In Simulink, these techniques are called solvers which are of two types: *variable-step* solver and *fixed-step* solver. In the official Simulink documentation [MathWorks, Inc., 2015c] we read the following:

"Both fixed-step and variable-step solvers compute the next simulation time as the sum of the current simulation time and a quantity known as the step size. With a fixed-step solver, the step size remains constant throughout the simulation. In contrast, with a variable-step solver, the step size can vary from step to step, depending on the model dynamics." ([MathWorks, Inc., 2010]: 592)

In choosing a solver a trade-off between accuracy and performance of the simulation is made. For example the *Runge-kutta-4* solver is more accurate than *Euler* solver but consumes more computational time. Since for models with a variable-step solver code-generation is not possible [MathWorks, Inc., 2015c],

<sup>&</sup>lt;sup>3</sup>Since Simulink has a notion of time (sample time) and it supports dynamic blocks with variable rates (for e.g. the switch block which can switch between data of variable sizes).

we will only support models with fixed-step solver with a fixed-step size in this thesis.

Because of scheduling issues and in order for a model with multi-rates (different sample times) to be simulated, some essential blocks for rate conversion (so called Rate-transition blocks) must be inserted between blocks with different sample times or else the simulation will fail with an output error message.

Code Generation The Embedded Coder [MathWorks, Inc., 2015a] takes Simulink models as an input and generates C/C++ source code optimized for embedded systems with configuration/customization options. The generated code can be optimized for different architectures and run on typical microcontrollers (MCU). Embedded Coder makes the Software-in-the-Loop (SIL) and Processor-in-the-Loop (PIL) verification and validation techniques possible. In the SIL technique the controller model is replaced by the generated code from the embedded coder (usually embedded in a s-function) and the behavior of the code is compared with the reference data achieved from MIL (described above). On the other hand, by the PIL technique the generated code is directly tested on a target processor, the code is compiled with a target compiler and downloaded to an evaluation board with the target controller. The PIL evaluation gives accurate details about the code size, the required RAM/ROM, the stack consumption over time and the execution times.

In our design flow (see Chap. 6), a *Virtual-Platform-in-the-Loop* (VPIL) is enabled in which the generated code after being mapped and run on a virtual-platform target processor (before deploying on the real hardware) is run in the loop with the environmental golden model in Simulink and an evaluation is done regarding functionality and execution times. Also other evaluations are possible with the help of this VPIL such as the code size the required RAM/ROM, stack/heap size analysis, interrupt analysis, tracing etc.

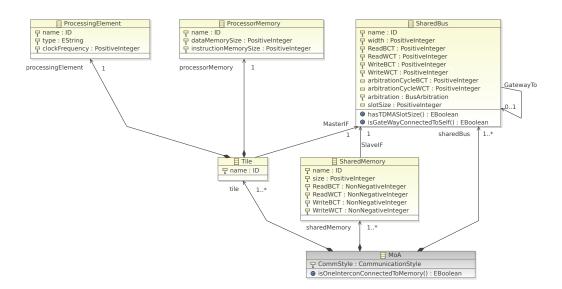

## 2.3 Timing Issues of MPSoCs

Current architectures e.g. in the automotive domain are witnessing a strong trend of increasing the number of processors in order to achieve increased performance and reduced Space Weight and Power (SWaP). In this thesis, we will consider architectures consisting of various processors (embedded processing elements, FPGAs, DSP) which are connected to storage resources through interconnects. We will use a similar terminology to that defined in [Rochange, 2011] to differentiate in the MPSoC between *storage resources* (e.g. memories, buffers and caches) which keeps information for a while (for several cycles or perma-

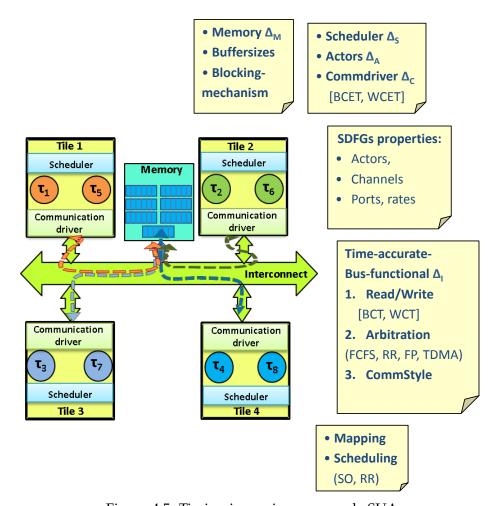

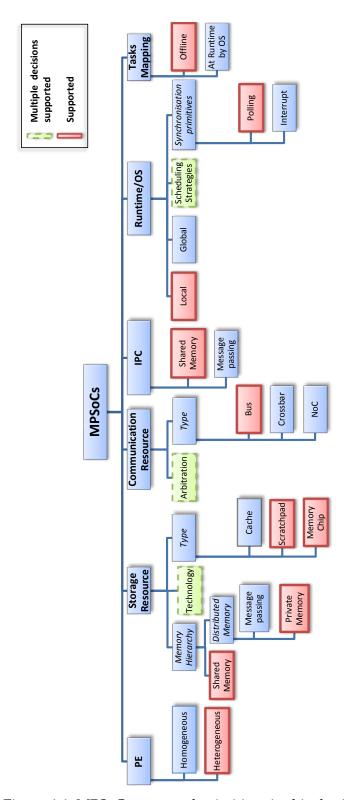

Figure 2.7: Decision tree of an MPSoC design

nently) and *communication resources* (buses, interconnects) where information is transfered from a sender to a receiver at each (number of) cycle(s).

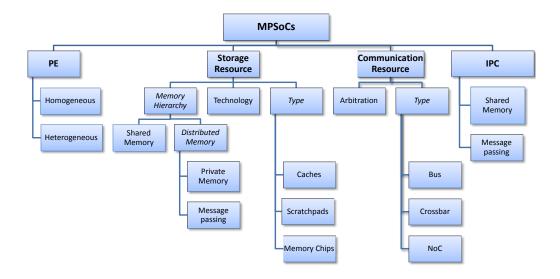

Fig. 2.7 shows the most relevant decisions to be met when developing an MPSoC application and which can influence its timing behavior. The processing elements (PE) could be homogeneous or heterogeneous where in the latter case for e.g. the instructions of some PE are optimized for a certain application domain. In this case, possible conversion<sup>4</sup> of data representation (referred to as endianess) should be performed when different PE are exchanging tokens over a communication resource.

Concerning storage resources, there are different *technology* types: *volatile* (such as SRAM and DRAM) where data are lost after power being unplugged and *non-volatile* (such as ROM or flash memory) where data remains conserved even if the power supply is no more existent [Lee and Seshia, 2012]. Storage resources (typically SRAM) which are used to store temporarily working data are called either *scratchpads* if they have a distinct set of addresses and the program is responsible for moving data into them or out of them to the distant memory [Lee and Seshia, 2012] or are called *caches* if they are able themselves to duplicate data existing in the distant memory in them and to synchronize (according to coherence strategy) or replace them (according to a replacement strategy) when needed [Lee and Seshia, 2012]. In addition, we can, depending on the hierarchy level, differentiate between *shared* memories and *distributed local* memories. A shared memory can be typically accessed by any PE in the

<sup>&</sup>lt;sup>4</sup>Since every communication partner in a heterogeneous platform can have different dataformating, data-formatting rules should be applied. These rules can be either defined globally or locally for every two communication partners [Gajski et al., 2009].

MPSoC. Whereas local memories can be either *private* memories with exclusive access to one PE or can be utilized to realize a message passing between a subset of existing PEs (typically between two of them).

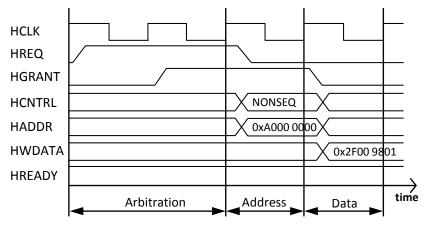

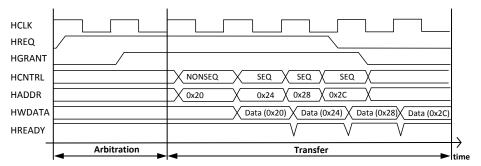

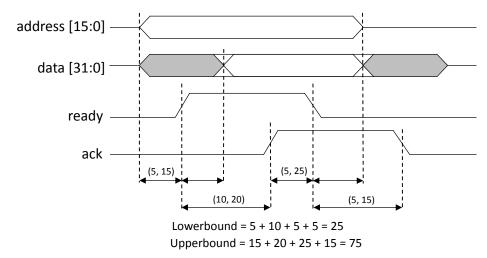

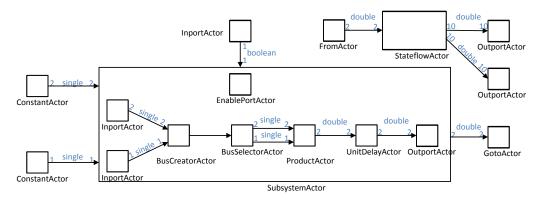

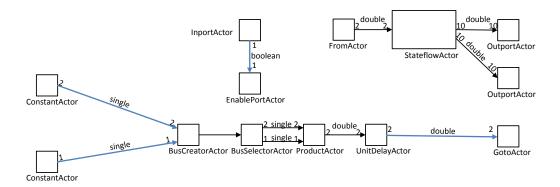

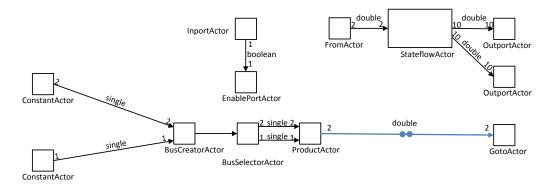

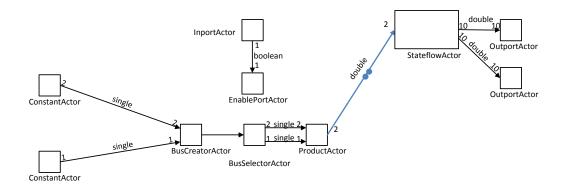

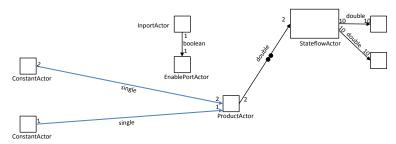

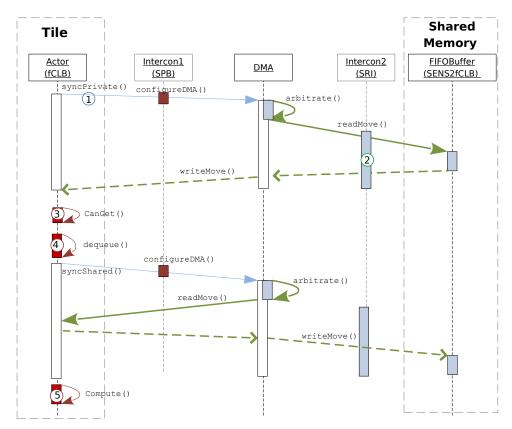

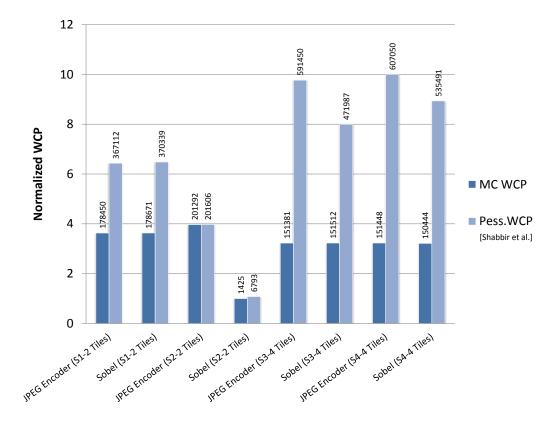

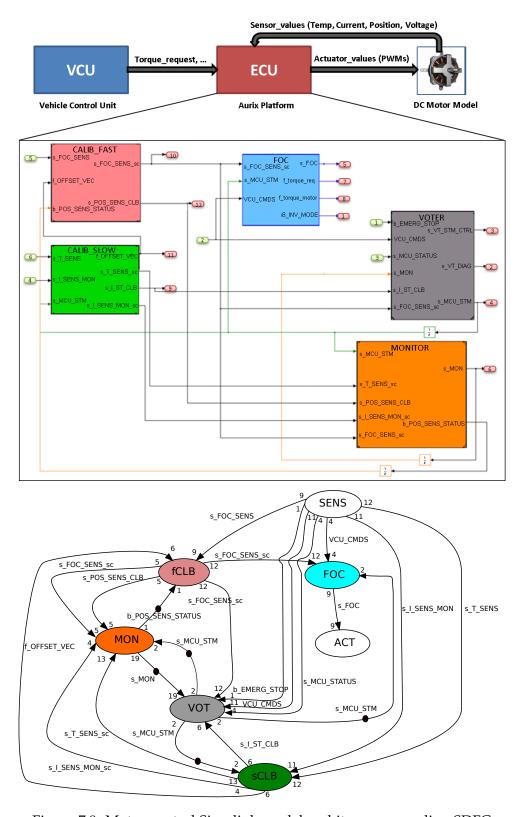

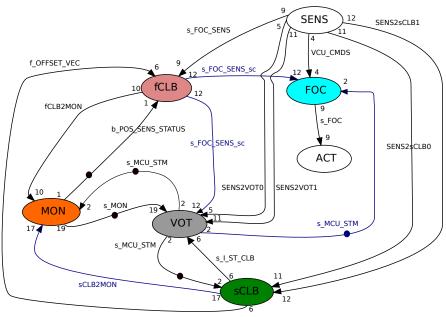

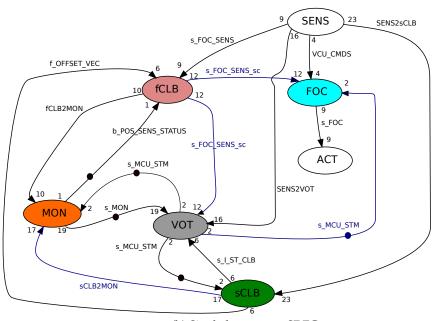

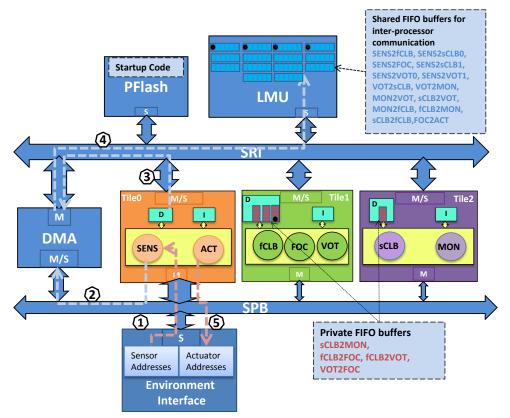

As to the communication resources in the MPSoC, different *types* of interconnects are available which can support *arbitrations* of various complexities. *Bus*-based communication in MPSoCs is still the state-of-the-art in many industrial domains (especially in the automotive architectures) and has proven to be efficient connecting a small numbers of PEs (see controller area network (CAN) bus [ISO11898-1, 2003]). For more flexibility *crossbars* were introduced (see Aurix platform [Infineon Inc., 2013]) which can improve performance by enabling one-way communication paths (without contention) between masters and slaves on the platform. With increasing the number of PEs in the platform, flexibility is required when connecting several PEs and in order to alleviate the contention bottleneck of traditional communication resources, *Network-On-Chip* (*NoC*) based interconnects were suggested [Bjerregaard and Mahadevan, 2006].