Fakultät II – Informatik, Wirtschafts- und Rechtswissenschaften Department für Informatik

# Fast and robust camera-based motion tracking using FPGAs in microrobotics

Dissertation zur Erlangung des Grades eines Doktors der Ingeneurswissenschaften (Dr.-Ing.)

von

Dipl.-Inform. Class Diederichs

Gutachter:

Prof. Dr. Sergej Fatikow Prof. Dr. Michaël Gauthier

Tag der Disputation: 28. November 2014

#### **Abstract**

In microhandling, the optical sensor is often the only way to obtain position information about tools and specimen. Optical microscopes are used to observe e.g. a manufacturing process. Image processing is extensively used if handling processes are fully automated. Based on the image sensor, objects are detected and classified. Additionally, the image sensor is often used as a motion tracking system for closed-loop positioning of tools (e.g. grippers or tips). There are several reliable algorithms available for motion tracking. Still, the speed and accuracy of a closed-loop positioning system is constrained by the quality of the sensor system used. In this case, the sensor system consists of the physical camera and the motion tracking system. From a control engineering point of view, the sensor system quality is defined by characteristics such as resolution and noise, but also by timing characteristics such as update-rate, latency and jitter. A closed-loop controller can perform significantly better if the sensor signal has a high update-rate and a low and predictable latency. A predictable and well known latency additionally allows for controller optimizations. High speed motion tracking is especially required in microrobotics because small objects have very low inertia and have high-speed dynamics.

Motion tracking using off-the-shelf computers and image-processing software has high latencies and high jitter. The achievable update-rates are up to 100 Hz. Experiments show that the update-rate has a high jitter, correlating with the used algorithm, the image content and the system load. Fast and robust motion tracking needs higher update-rates and a predictable runtime, thus a very low jitter. Therefore, for fast and robust motion tracking, different techniques are needed.

Different approaches to improving the timing performance of motion tracking are exploited. First, a real-time operating system was used to control the scheduling of tasks. This ensured that the motion tracking would not be preempted by other processes running on the computer. Secondly, a hardware-software co-design strategy was used: An FPGA-implementation of a tracking algorithm was utilized on an embedded system. Using an FPGA, a major part of the image processing can be done in parallel performing hardware blocks. Additionally, a stream mode implementation can be used. Stream processing does not operate on an image that is available in memory, but on single pixels that are sequentially streamed through the hardware. Therefore, the image can be directly processed while its data is acquired from the camera chip and, instead of written back to memory, directly

iv Abstract

passed to the next operation. Such a pipelined design reduces the latency of image processing significantly.

A novel hardware implementation of the Binary Large Object (BLOB) detection approach was implemented to address the above mentioned timing characteristics. This implementation is superior to state of the art hardware implementations in terms of speed, controllable objects and resource utilization. Additionally, the implementation calculates novel BLOB features that allow for better object classification.

While the real-time operating system improved all characteristics slightly, the FPGA implementation showed huge improvements especially on latency, jitter and predictability. The achievable update-rate was improved to 1.8 Ghz. The latency was improved to exactly one camera frame (exposure time plus transfer time), which is the best theoretical value. Also, the jitter was improved by more than one order of magnitude, thus allowing for a high predictable update-rate and latency.

The developed FPGA-solution was integrated into a microhandling station to evaluate the performance. In this microhandling station, two mobile microrobots were cooperatively performing pick-and-place operations with 50 µm objects. The robots had no internal position sensors and needed to be controlled by optical motion tracking. Prior to the integration, the robots had been tracked by PC-based motion tracking. With the integration it was possible to reduce the time of a single pick-and-place operation from 15 seconds to less than two seconds. To show the flexibility of the developed algorithm, the prototype was also applied to a traffic-sign recognition system.

## Zusammenfassung

In Mikromontagesystemen werden Positionen von Werkstücken und Manipulatoren oft durch Mikroskope und Kameras erfasst und ausgewertet. Dabei werden verschiedene berechnungsintensive Bildverarbeitungsalgorithmen genutzt, um Werkstücke zu erkennen und zu klassifizieren oder um Werkzeuge wie Greifer, Spitzen oder Kanülen zu positionieren. Wird die Bildverarbeitung als Sensor in die Positionsregelung eines Manipulators eingebunden, wird dies Visual Servoing genannt. Zu diesem Zweck sind verschiedene Algorithmen in den letzten Jahrzehnten entwickelt worden. Die Geschwindigkeit und die Positioniergenauigkeit einer Regelung sind abhängig von dem eingesetzten Sensorsystem, das bei Visual Servoing aus Kamera und Bildverarbeitungssystem besteht. Die Qualität eines Sensors wird über Werte wie Auflösung, Signalrauschen und Linearität definiert. Es sind aber auch zeitliche Merkmale wie Wiederholrate, Latenz und Jitter von Bedeutung. Hat ein Signal eine hohe Wiederholrate, eine geringe Latenz und ein vorhersagbares Latenzverhalten, kann eine Regelung erheblich schneller und, durch die Vorhersagbarkeit der Sensorlatenz, genauer arbeiten. Insbesondere in der Mikrorobotik werden Hochgeschwindigkeitssensoren benötigt, da Mikroaktoren kleine Massen und daher eine hohe Dynamik aufweisen.

In der Arbeit wird gezeigt, dass die oft eingesetzten Standard-PCs mit Bildverarbeitungssoftware eine hohe Latenz aufweisen und die Wiederholrate sowie die Latenz starken Schwankungen unterliegt. Die erreichbaren Wiederholraten sind, je nach Algorithmus, im Bereich von 100Hz und zudem stark abhängig von der Gesamtlast des Systems.

Es wurden verschiedene Ansätze untersucht, die drei Merkmale Wiederholrate, Latenz und Jitter zu verbessern. Als bester Ansatz hat sich die Benutzung eines Field Programmable Gate Arrays (FPGA) herausgestellt. Auf einem FPGA kann ein großer Teil der Bildverarbeitung in parallel arbeitenden Hardwareblöcken durchgeführt werden. Zudem kann eine Datenstromimplementierung genutzt werden, die bereits arbeitet während der Sensor ausgelesen wird, was zu einer verbesserten Latenz führt. Durch die Nutzung bekannter sowie neu entwickelten BLOB-Eigenschaften kann ein erkanntes Objekt klassifiziert werden.

Eine neuartige Hardware-Implementierung des Binary Large OBject (BLOB) Extraction Algorithmus wurde entwickelt, die alle drei Merkmale im Vergleich zu einer PC-Lösung signifikant verbessern. Die Klassifizierung wurde zunächst mit statischen Grenzen für die verschiedenen Eigenschaften implementiert. Der entwickelte Prototyp wurde in eine Mikrohandhabungsstation integriert und konnte

dort die Prozesszeit einer einzelnen Pick and Place Operation von 15 Sekunden auf unter 2 Sekunden verbessern. Der Prototyp wurde weiterhin in einem System zur Straßenschilderkennung eingesetzt.

## **Acknowledgements**

The presented work has been carried out at the Division Microrobotics and Control Engineering (AMiR) at the University of Oldenburg, Germany, headed by Prof. Dr.-Ing. Sergej Fatikow. I would like to express my gratitude to Prof. Dr. Fatikow for supervising my Ph.D. thesis, the division's excellent laboratory equipment as well as the confidence he had in my work. I highly appreciate the freedom I had during the time of my doctorate. Furthermore, I would like to thank Prof. Dr. Michaël Gauthier for refereeing this dissertation.

I would like to thank all of my colleagues for the excellent team work. I especially thank Daniel Jasper for all the fruitful discussions, the joint work and the support he gave me even after he left the team.

I would like to thank my parents Dörte and Wolfgang Diederichs for their constant support throughout my life. Finally and most importantly, I would like to thank my family, my wife Lotte and my two children Emma and Marieke for their moral support throughout the years. Without your support, I would not be where I am today.

# **Contents**

| Α  | bstract                                                                                                                                                                                                                                                                                                                                                                                                             | iii                                                                        |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Z  | usammenfassung                                                                                                                                                                                                                                                                                                                                                                                                      | V                                                                          |

| Α  | cknowledgements                                                                                                                                                                                                                                                                                                                                                                                                     | vii                                                                        |

| Li | ist of Figures                                                                                                                                                                                                                                                                                                                                                                                                      | X                                                                          |

| 1  | Introduction 1.1 Goals                                                                                                                                                                                                                                                                                                                                                                                              | 1<br>2<br>3                                                                |

| 2  | State of the art  2.1 Object tracking in microrobotics                                                                                                                                                                                                                                                                                                                                                              | 5<br>6<br>14<br>15<br>17                                                   |

| 3  | A novel FPGA implementation of the BLOB extraction algorithm  3.1 Requirements and goals 3.2 Features 3.2.1 Weighted center of gravity 3.2.2 Bounding polygon 3.2.3 Principal component analysis based features  3.3 Equivalence handling 3.3.1 Implementation  3.4 Architecture 3.4.1 Parameters and RAM sizes  3.5 Further throughput improvement  3.6 Implementation and test strategy 3.6.1 Waveform simulation | 23<br>25<br>27<br>27<br>28<br>29<br>32<br>36<br>49<br>58<br>62<br>64<br>64 |

|    | 3.6.2 Hardware in the Loop                                                                                                                                                                                                                                                                                                                                                                                          | 66                                                                         |

x Contents

|   |       | 3.6.3 Resource usage and throughput                        | 71  |

|---|-------|------------------------------------------------------------|-----|

|   | 3.7   | Conclusions                                                |     |

| 4 |       | lidation                                                   | 77  |

|   | 4.1   | Test setup                                                 | 77  |

|   | 4.2   | Prototype                                                  | 78  |

|   | 4.3   | Update-rate jitter                                         | 82  |

|   | 4.4   | Latency and latency jitter                                 | 93  |

|   |       | Conclusions                                                |     |

| 5 | Ap    | plications                                                 | 111 |

|   | 5.1   | Automated handling of microspheres                         | 111 |

|   |       | 5.1.1 Comparison of software-based and FPGA-based tracking |     |

|   |       | 5.1.2 Tracking of multiple robots                          | 118 |

|   |       | 5.1.3 Distortion correction                                |     |

|   |       | 5.1.4 Sensor accuracy evaluation                           |     |

|   |       | 5.1.5 Closed loop performance                              |     |

|   |       | 5.1.6 Conclusions                                          |     |

|   | 5.2   | Traffic sign recognition                                   |     |

|   |       | Conclusions                                                |     |

| 6 | Coi   | nclusions and outlook                                      | 133 |

|   |       | Conclusions                                                | 134 |

|   |       | Outlook                                                    |     |

| В | iblio | graphy                                                     | 137 |

# List of Figures

| 2.1  | Logical layout of a hardware thresholding operation             | Ö  |

|------|-----------------------------------------------------------------|----|

| 2.2  | Simplified logic layout of a hardware local filter              | 11 |

| 2.3  | Control signals of stream-based image-processing                | 13 |

| 2.4  | Control signals of stream-based image-processing (2)            | 13 |

| 2.5  | Neighborhood for connected component labeling                   | 15 |

| 2.6  | Two-pass connected component labeling algorithm                 | 17 |

| 2.7  | The single-pass architecture used by Bailey and Johnston (2007) | 20 |

| 3.1  | Example of a bounding octagon                                   | 28 |

| 3.2  | Image of a micro-gripper                                        | 32 |

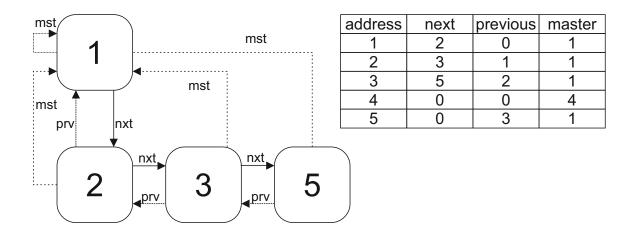

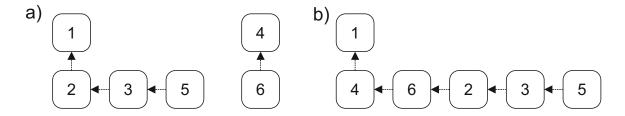

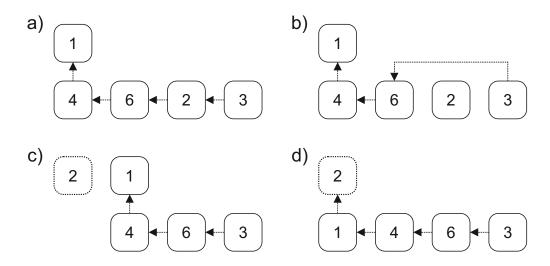

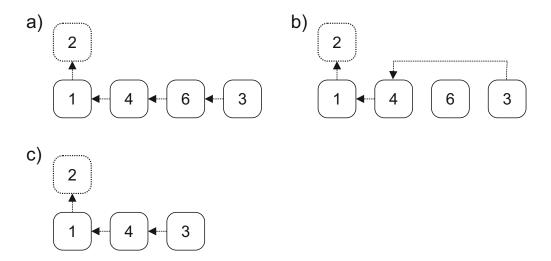

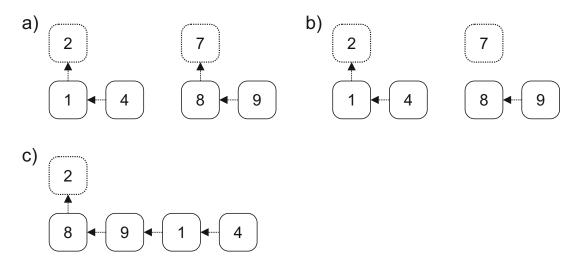

| 3.3  | Example of a subset in the disjoint set                         | 33 |

| 3.4  | Union of two subsets in a disjoint set                          | 34 |

| 3.5  | Master exchange of a subset in the disjoint set                 | 35 |

| 3.6  | Shrinking of a subsection in a disjoint set                     | 36 |

| 3.7  | Union of two subsets that both have a finished master           | 37 |

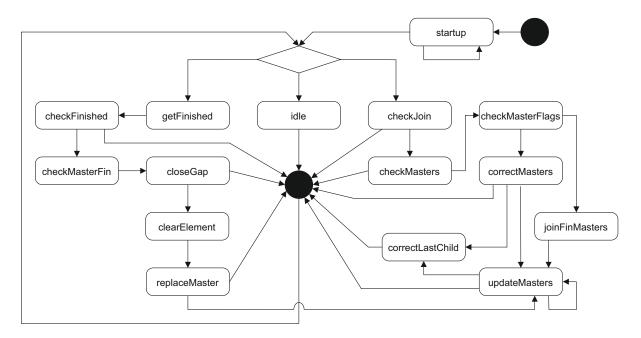

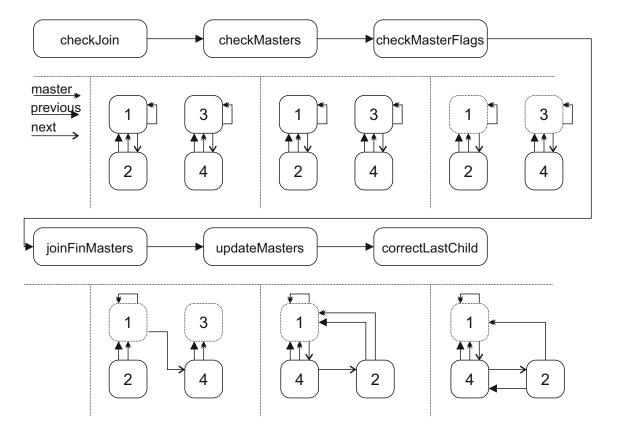

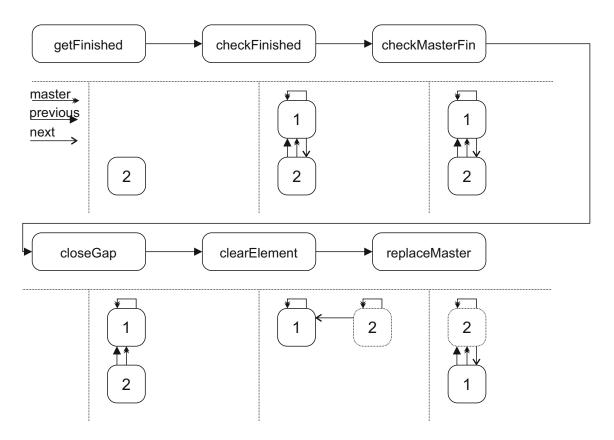

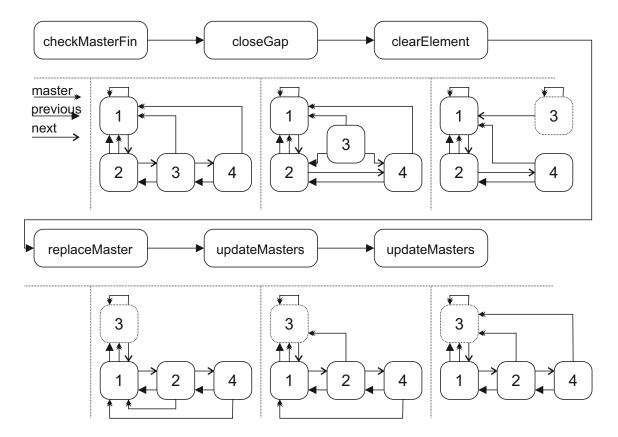

| 3.8  | State machine of the equivalence handling hardware system       | 38 |

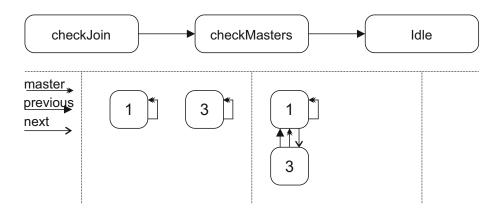

| 3.9  | Union of two subsets consisting of only one element             | 40 |

| 3.10 | Union of two subsets consisting of two elements each            | 41 |

| 3.11 | Union of two subsets consisting of two elements each where both |    |

|      | masters are finished                                            | 42 |

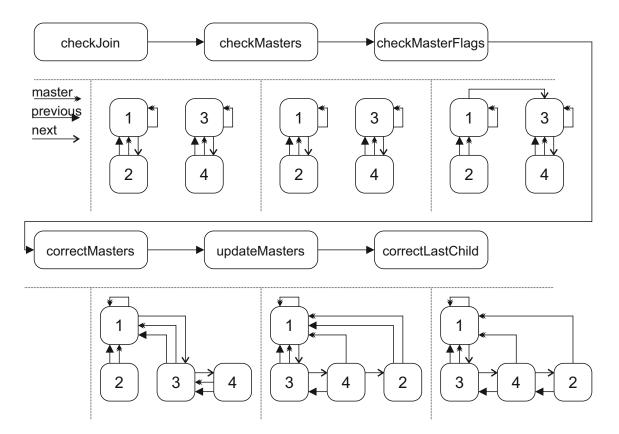

|      | Switching of masters when a child is finished                   | 43 |

|      | Switching of masters in a larger subset                         | 45 |

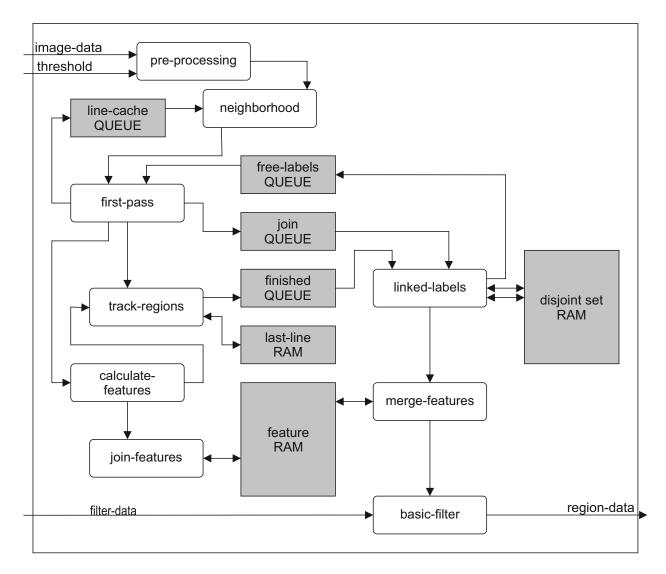

|      | Architecture of the parallel approach algorithm                 | 50 |

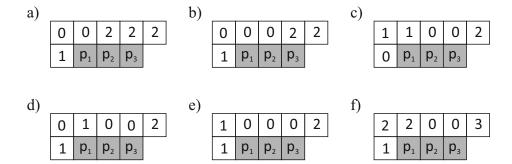

|      | First-pass neighborhood of the parallel approach                | 52 |

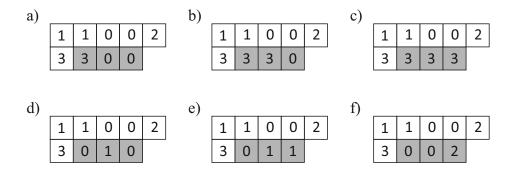

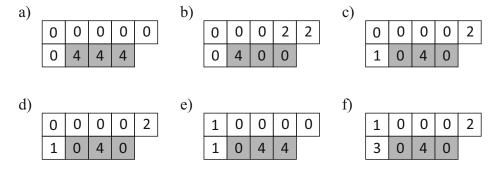

|      | Label assignments during the first pass                         | 53 |

|      | New label assignments during the first pass                     | 53 |

|      | Different join situations                                       | 54 |

|      | Advanced first pass neighborhood for nine pixels                | 63 |

|      | Architecture of the waveform simulation                         | 66 |

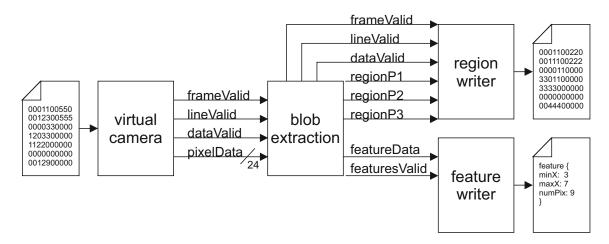

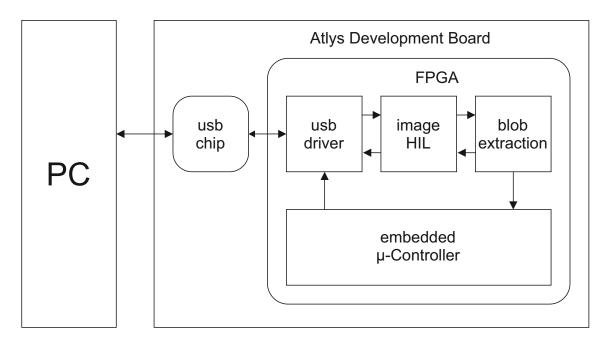

|      | Architecture of the hardware in the loop system                 | 67 |

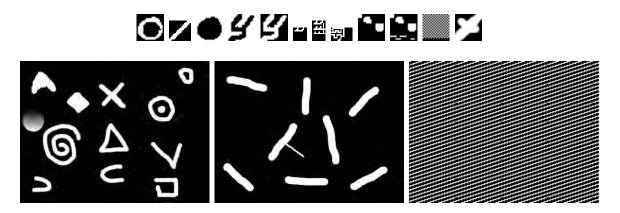

|      | Different test images                                           | 69 |

| 3.23 | Randomly generated test images                                  | 69 |

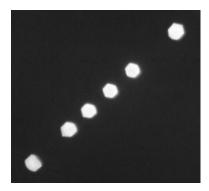

| 4.1  | Image observed by the test setup                                | 78 |

| 4.2  | Setup for the validation of the system timing (FPGA)                   | 79  |

|------|------------------------------------------------------------------------|-----|

| 4.3  | Setup for the validation of the system timing(PC)                      | 79  |

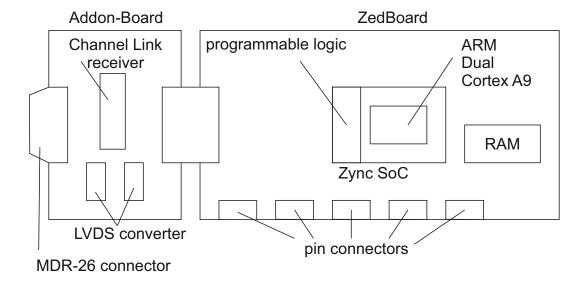

| 4.4  | Overview of the hardware platform used                                 | 81  |

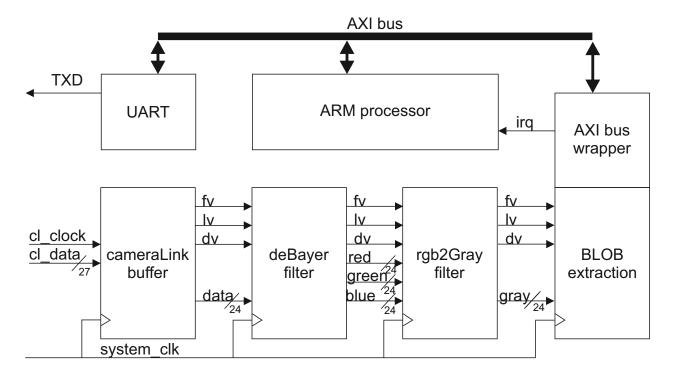

| 4.5  | Overview of the FPGA design used                                       | 83  |

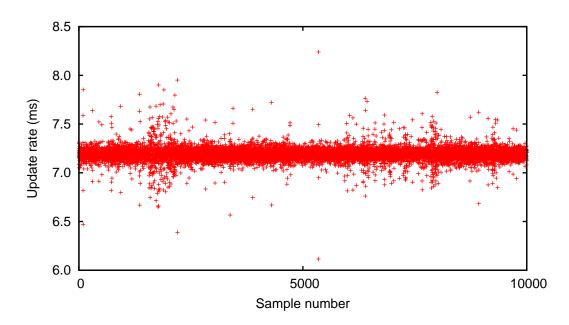

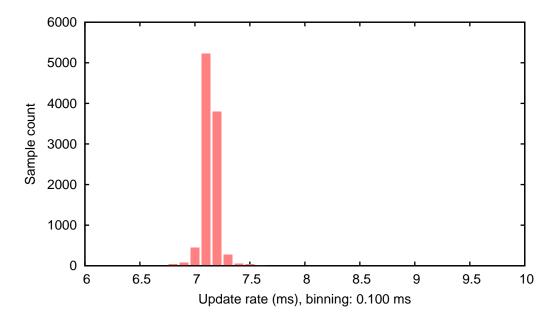

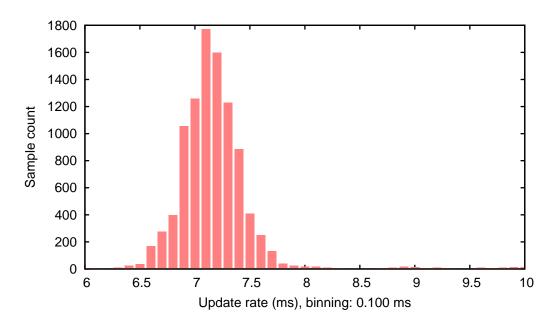

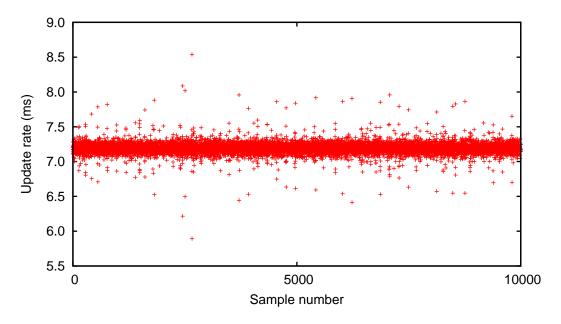

| 4.6  | Update rate distribution of one object                                 | 84  |

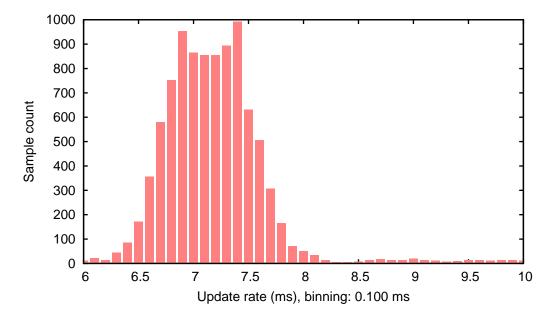

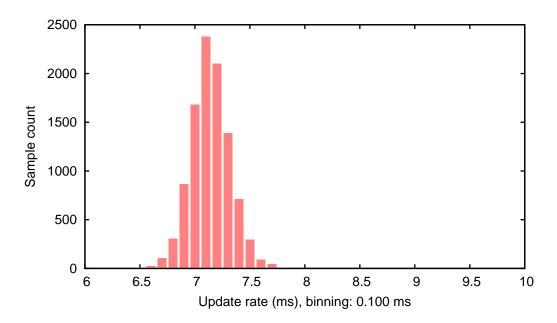

| 4.7  | Update rate histogram of one object                                    | 84  |

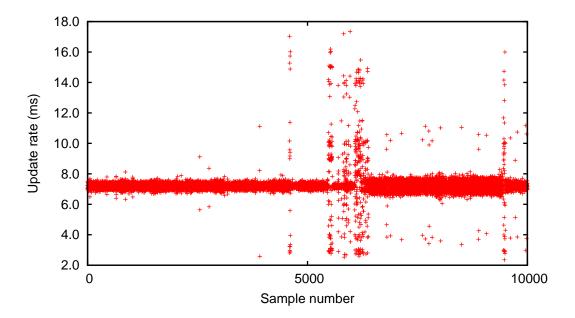

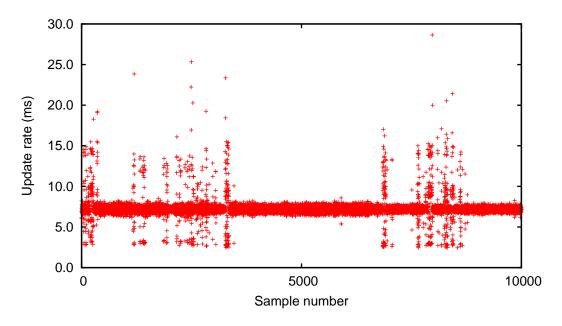

| 4.8  | Update rate distribution of one object with the full processor load .  | 85  |

| 4.9  | Update rate histogram of one object with full processor load           | 86  |

| 4.10 | Update rate distribution of eight objects with a full processor load . | 87  |

| 4.11 | Update rate histogram of eight objects with a full processor load      | 87  |

| 4.12 | Update rate distribution of one object with a real-time extension .    | 88  |

| 4.13 | Update rate histogram of one object with a real-time extension         | 89  |

| 4.14 | Update rate distribution of eight objects with a real-time extension   |     |

|      | and a full processor load                                              | 90  |

| 4.15 | Update rate histogram of eight objects with a real-time extension      |     |

|      | and a full processor load                                              | 90  |

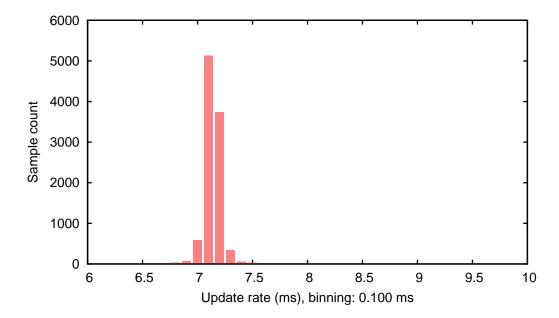

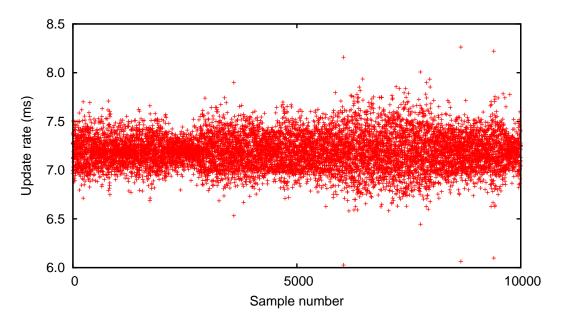

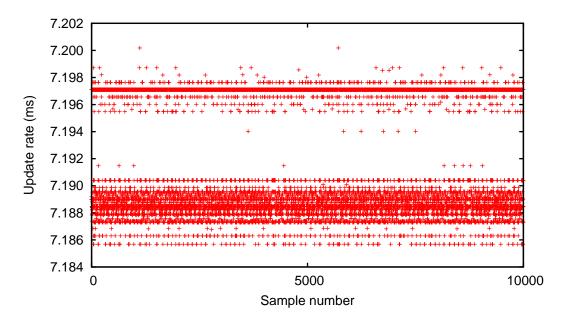

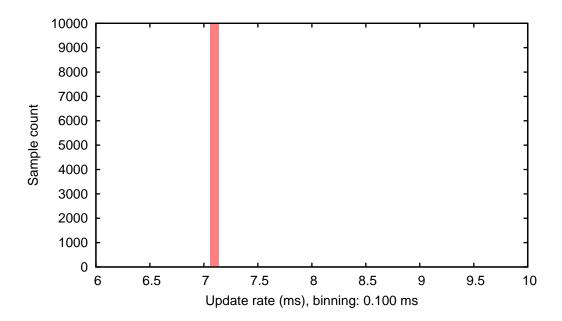

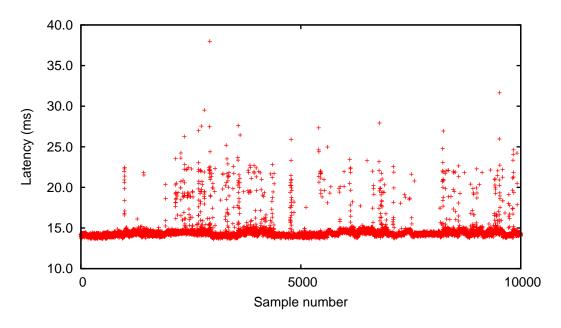

| 4.16 | Update rate distribution of eight objects tracked with FPGA            | 91  |

| 4.17 | Update rate histogram of eight objects tracked with FPGA               | 92  |

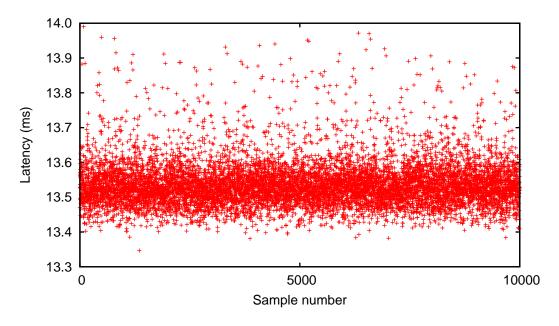

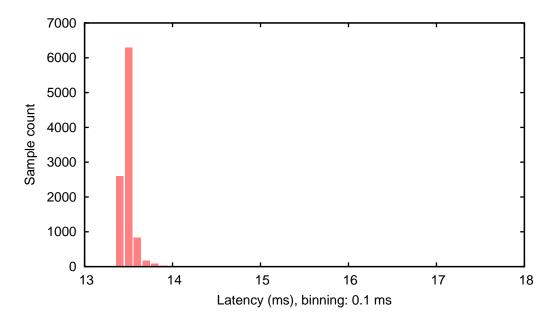

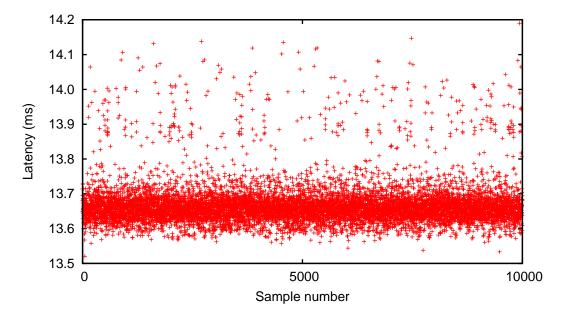

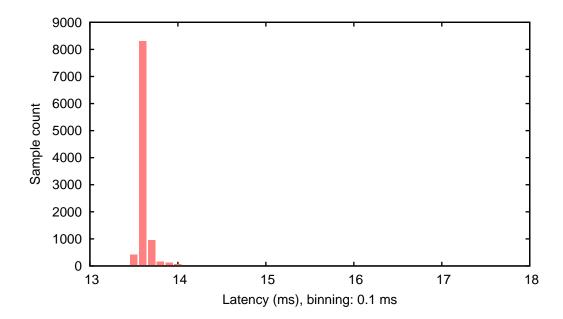

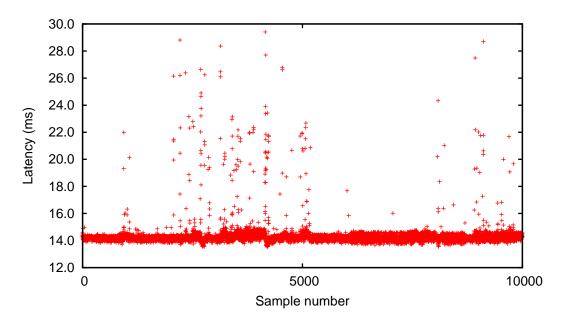

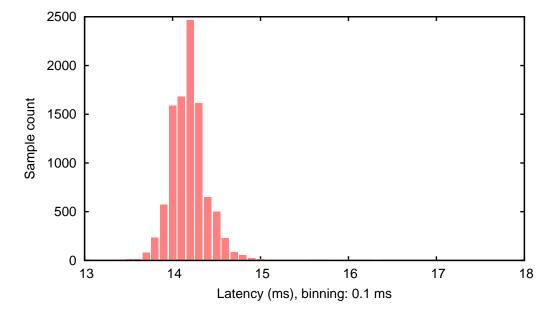

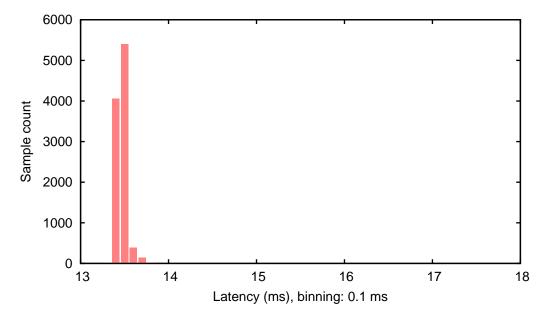

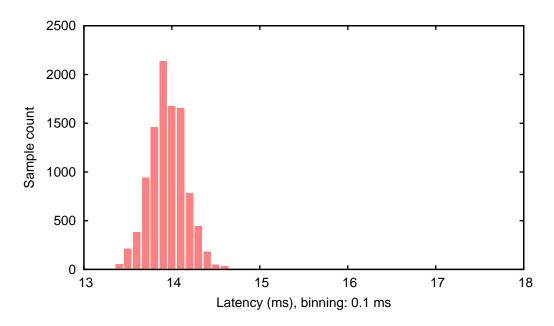

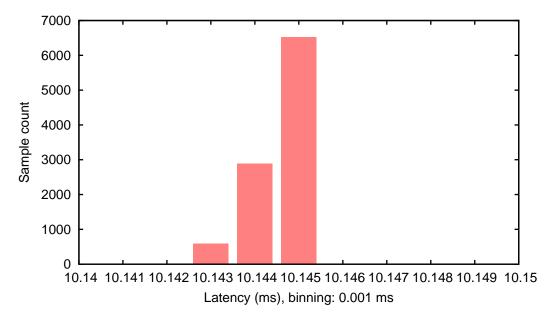

| 4.18 | Latency distribution of one object                                     | 94  |

| 4.19 | Latency histogram for one object                                       | 95  |

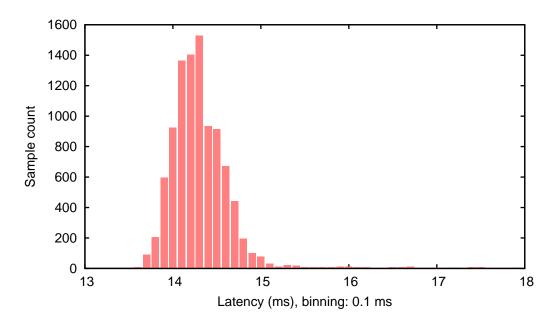

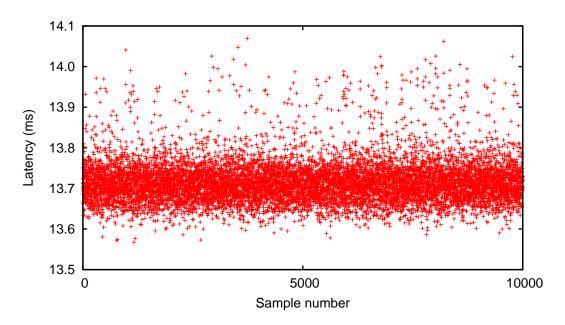

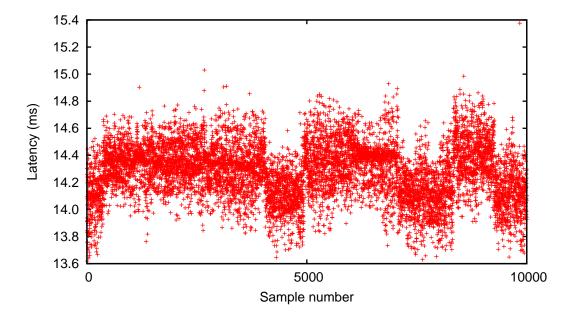

| 4.20 | Latency distribution of eight object                                   | 95  |

| 4.21 | Latency histogram for eight objects                                    | 96  |

| 4.22 | Latency distribution of one object with a full processor load          | 97  |

| 4.23 | Latency histogram for one object with a full processor load            | 97  |

| 4.24 | Latency distribution of eight objects with a full processor load       | 98  |

| 4.25 | Latency histogram for eight objects with a full processor load         | 98  |

| 4.26 | Latency distribution of one object with a real-time extension          | 99  |

| 4.27 | Latency histogram for one object with a real-time extension            | 99  |

| 4.28 | Latency distribution of eight objects with a real-time extension       | 100 |

| 4.29 | Latency histogram for eight objects with a real-time extension         | 100 |

| 4.30 | Latency distribution of one object with a real-time extension and a    |     |

|      | full processor load                                                    | 101 |

| 4.31 | Latency histogram for one object with a real-time extension and a      |     |

|      | full processor load                                                    | 102 |

| 4.32 | Latency distribution of eight objects with a real-time extension and   |     |

|      | a full processor load                                                  | 102 |

| 4.33 | Latency histogram for eight objects with a real-time extension and     |     |

|      | a full processor load                                                  | 103 |

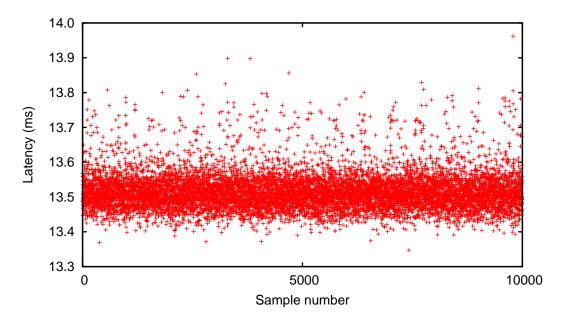

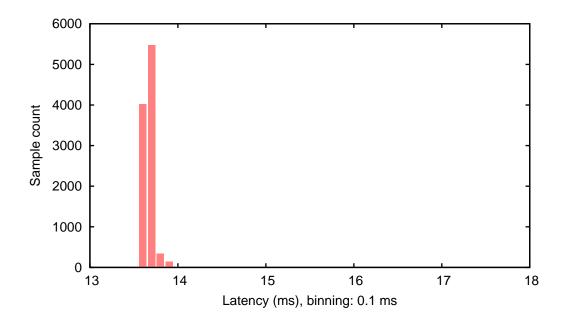

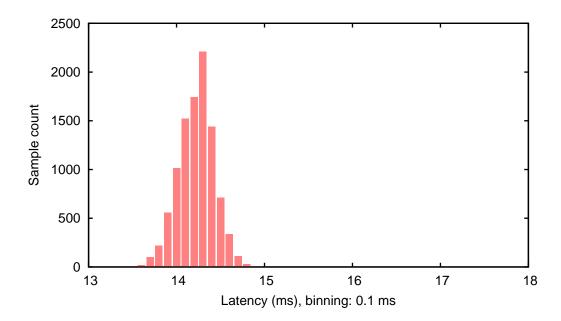

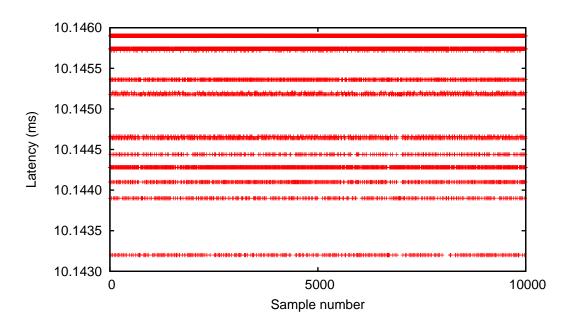

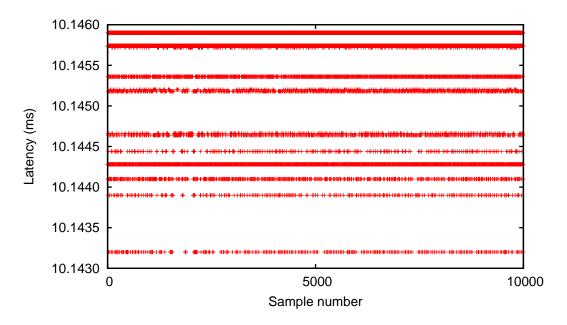

|      | Latency distribution of one object tracked with FPGA                   |     |

|      | Latency histogram for one object tracked with FPGA                     |     |

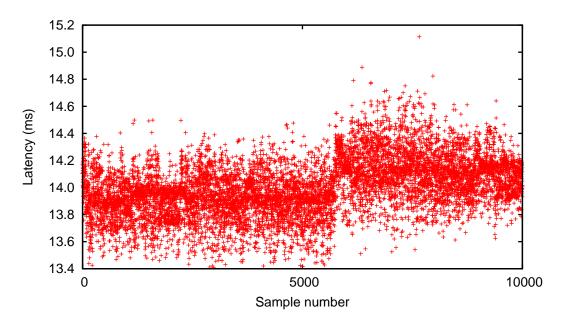

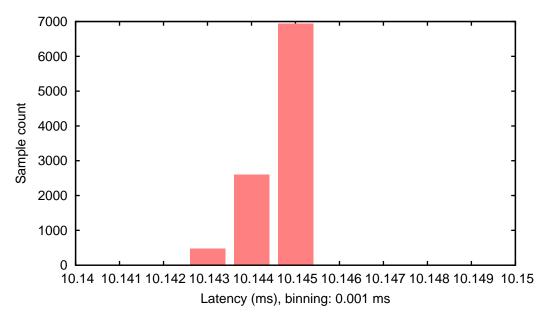

| 4.36 | Latency distribution of eight objects tracked with FPGA                | 105 |

| 4.37 | Latency histogram for eight objects tracked with FPGA 105                |

|------|--------------------------------------------------------------------------|

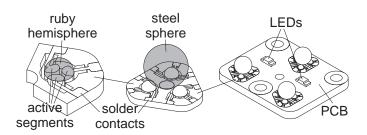

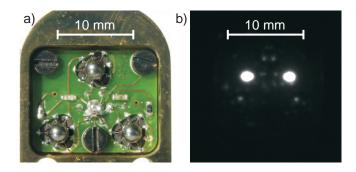

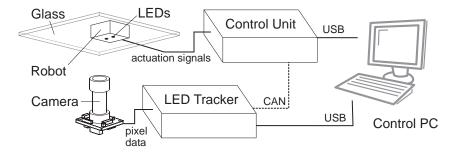

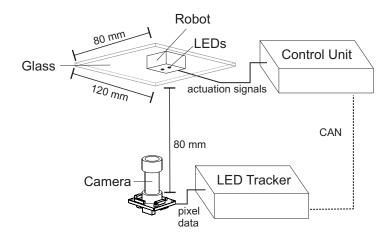

| 5.1  | Mobile robot actuation unit                                              |

| 5.2  | Bottom view of the tracked mobile robot                                  |

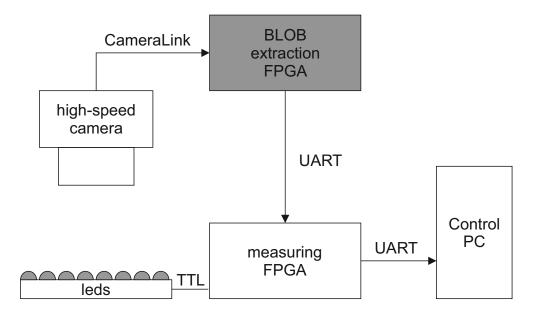

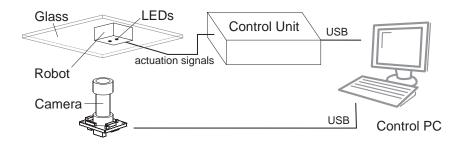

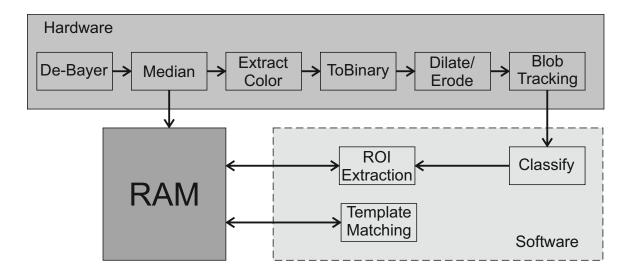

| 5.3  | Architecture of the tracking system before the FPGA deployment $$ . 113  |

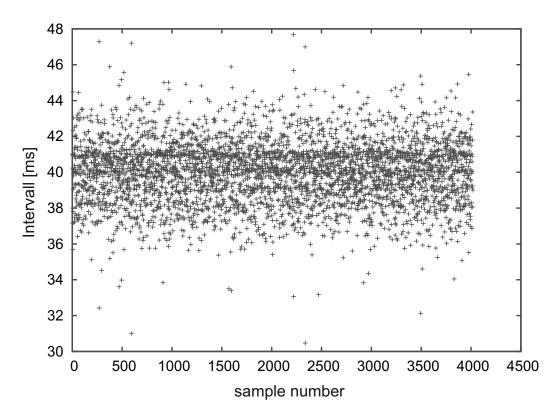

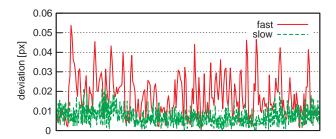

| 5.4  | Update rate deviation of software-based robot tracking $\dots \dots 114$ |

| 5.5  | Latency of software-based robot tracking                                 |

| 5.6  | Architecture of the tracking system using an FPGA                        |

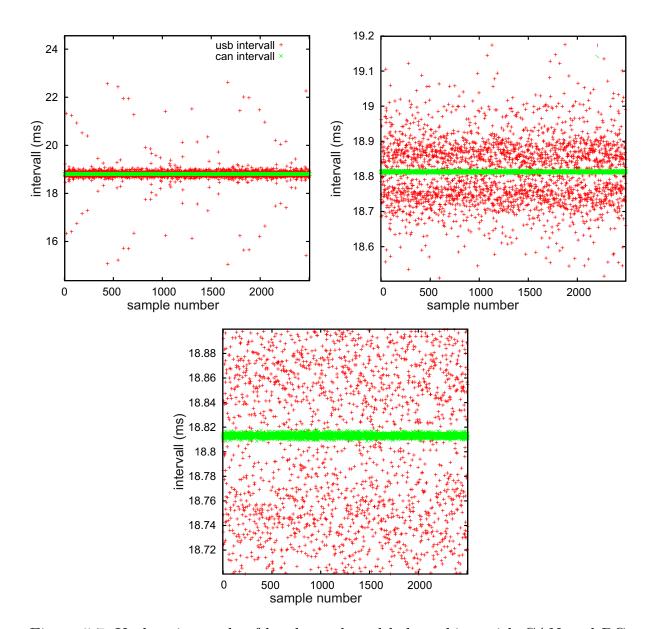

| 5.7  | Update intervals of hardware-based led tracking                          |

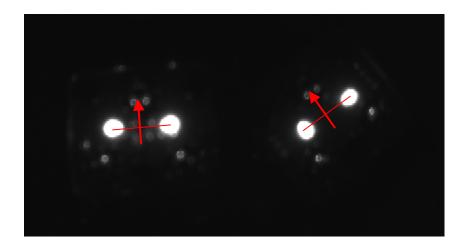

| 5.8  | Mapping of two region centers to robot position and angle 119            |

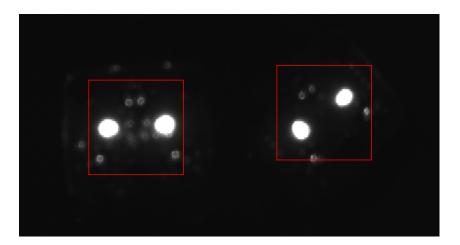

| 5.9  | Robot tracking performed in alternating ROIs                             |

| 5.10 | Architecture and dimensions of the multiple robot tracking system 120    |

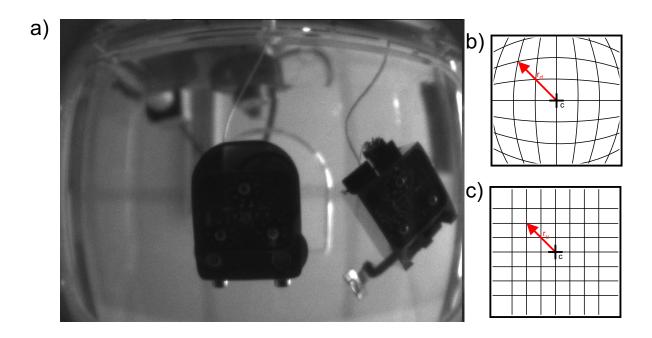

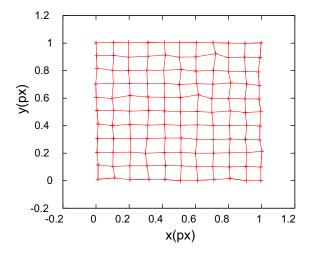

| 5.11 | Distorted image taken by the camera beneath the glass surface $121$      |

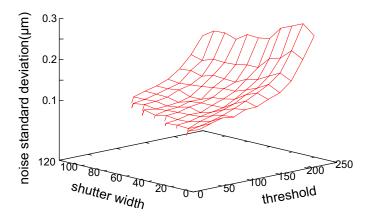

| 5.12 | Noise standard deviation at the lens center                              |

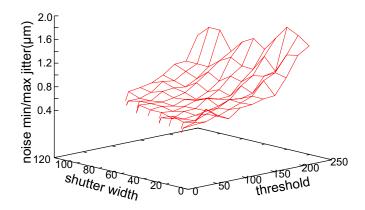

| 5.13 | Noise maximum deviation at the lens center                               |

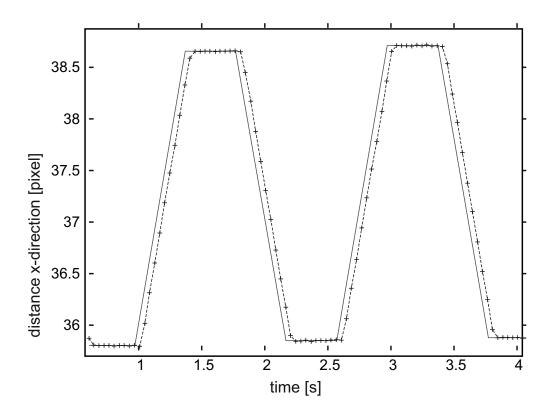

| 5.14 | Sensor linearity of one square pixel                                     |

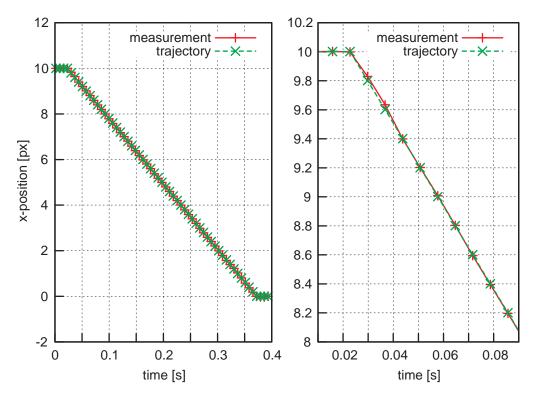

| 5.15 | Trajectory control algorithm for mobile robots                           |

| 5.16 | Error over time while driving along a linear trajectory                  |

| 5.17 | Measurements of a linear trajectory                                      |

| 5.18 | Different German traffic signs                                           |

| 5.19 | Traffic sign recognition architecture                                    |

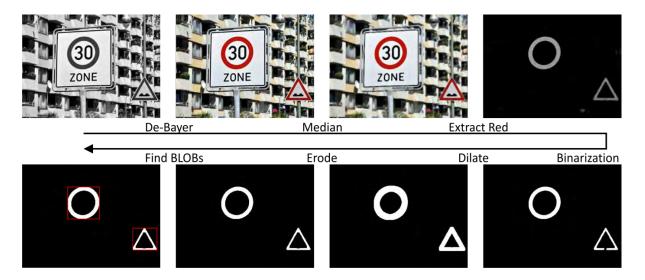

| 5.20 | Traffic sign recognition hardware chain example                          |

#### 1 Introduction

Image processing and motion tracking is a key concept in micro- and nanorobotics. In optical motion tracking, the camera is used as a sensor to determine the motion of a tool or object in the view of the camera. The information of motion tracking is often used as input for position controllers. The position controllers need to rely on the correctness of the information from motion tracking. However, not only the correctness of the position is of importance, but also the age of the sensor signal. If the sensor signal is too old, the motion controller works with outdated information. If the age of the sensor signal is deterministic and well-known, the controller can, with some effort, compensate for it. If the age of the sensor data is unknown or has a large jitter, the motion controller cannot compensate for it. Especially jitter in the position update-rate and the update latency can lead to incorrect behavior in the motion controller. A sensor signal with large jitter and unknown latency will lead to a decreased positioning speed. On the one hand, large unknown latencies will cause the controller to overshoot the target position, resulting in an oscillating position behavior. It can even be the case that the target position cannot be reached with the desired accuracy. This has to be compensated for; either by using less accurate target positions or a lower positioning speed.

Most camera systems used for motion tracking are consumer- or industry cameras that are used with off the shelf computers and software-based image-processing. In motion tracking for microrobotics, this constellation can be found in almost every manipulation setup.

Such a setup has the problematic characteristics described above. Firstly, it is unknown how long the sensor latency is. The sensor latency consists of the camera's exposure time, the time needed to transfer the data to the PC, the time needed by image-processing and the communication to the motion controller.

While some of the latency parts are deterministic and can be analyzed, others are not. The exposure time of the camera is dependent on the illumination and the auto-exposure behavior. For most cameras, the exposure time can be set to a fixed value. The transfer time from the camera to the PC is dependent on the interface used and its real-time capabilities.

However, with the common operating systems the latency that is caused by image processing is highly dependent on the hardware used and is influenced by other processes running on the PC.

Four problems can be identified for PC-based image processing:

- The latency of a PC-based motion tracking system is long and not deterministic

- The update-rate of a PC-based motion tracking system is limited and not deterministic

- The timing behavior of a PC-based motion tracking system is influenced by other processes running on the same PC.

- The nondeterministic behavior of PC-based motion tracking systems results in longer and less accurate positioning steps.

While some of these problems can be resolved using real-time operating systems, others remain. Additionally, the image processing throughput (i.e. update-rate) is often increased by using regions of interest (ROIs) in an image. The camera is configured in a way that only a small sub-image of the sensor is transferred to the PC and used for image processing. While the usage of ROIs increase the update-rate, the nondeterministic calculation behavior remains. Furthermore, using a ROI limits the area where other image-processing steps are performed and is often not feasible.

This work aims to improve the timing in positioning steps using image-based motion tracking.

As software-based image-processing running on PCs suffers from several problems, one goal is to develop an object detection system based on deterministic hardware. FPGAs are well suited for highly parallel, deterministic computations. Image processing on FPGAs is widely used for preprocessing and filtering steps. These operations are well understood and several deterministic, highly parallel FPGA implementations exist that can facilitate high speeds.

However, deterministic, robust high speed motion tracking systems are not yet state of the art.

#### 1.1 Goals

The overall goal of this work is to improve the speed and robustness of positioning steps during camara-based positioning. To overcome the timing problems that exist with PC-based image processing, an FPGA system for robust high speed motion tracking can be used. The goal of this work is to develop such a system with the following characteristics:

- High throughput: The tracking system must allow for high update-rates. As goal, the fastest speed of the CameraLink protocol (680 MB/s) should be possible.

- Low latency: The computational time for motion tracking should be as low as possible.

- Deterministic latency: The latency must be predictable and must not be influenced by the image content; an image with no objects shall have the same latency as an image with several objects. Furthermore, noise should have no impact on the latency.

- Robustness: The tracking system must continue to work with a deterministic timing behavior for unexpected images such as high and unexpected noise or images with unexpected highly numbers or sizes of objects.

A secondary goal is to test the tracking system and compare the results to PC-based image processing. Furthermore, a real-time operating system shall be evaluated with the same test setup to analyze whether the FPGA system has benefits over software-based tracking if a real-time operation system is used.

The last goal is to deploy the system in a microrobotic handling cell and evaluate a possible performance gain.

#### 1.2 Outline / Author's contribution

The thesis contributes to the advancement of the closed-loop motion control for automated microhandling and microassembly and is structured in five chapters following this introduction.

chapter 2 describes the current state of the art for automated microhandling and FPGA-based image processing. For FPGA-based image processing, different implementation paradigms must be taken into consideration when deterministic behavior is the aim. The chapter gives an overview of the differences between software-based computations for image processing and hardware based approaches. An overview of FPGA-based object detection approaches is given. Special attention is given to the binary large object detection algorithm that is the base of the developed tracking system.

A novel implementation of the binary large object detection algorithm is introduced in chapter 3. The implementation choses a novel approach. This allows for a high throughput on the one hand, and robustness and deterministic timing behavior on the other hand. The implementation can reach throughputs of up to 1.8 GB/s (depending on the FPGA used) while being robust and deterministic in the timing behavior. The system is tested with different test images, including images consisting only of noise and images consisting of several thousand objects.

In chapter 4, the tracking system is tested and compared against software-based image processing. A test architecture was developed that measures the response time of a tracking system by using a dedicated FPGA for the measurement. A real-time operating system was used to improve the performance of the PC-based tracking. Results show that a real-time system improves the timing behavior of PC-based image processing significantly, but the FPGA system is magnitudes better concerning the update-rate deviation, can handle higher data rates and has a lower latency than PC-based systems.

Two different applications that use the FPGA-tracking implementation are described in chapter 5. The focus is on the improvement of an existing microhandling cell. The microhandling cell was upgraded with the FPGA-based tracking algorithm. The closed-loop positioning speed could be improved by one magnitude. A second application is presented to underline the possibilities the FPGA-based object detection provides in other fields. The second application describes a low-cost traffic sign recognition system that aims at low power consumption.

The final chapter 6 contains a conclusion and an evaluation of this work's impact on the speed, throughput and industrial applicability of automated microhandling and microassembly. An outlook describes future steps extending this work.

### 2 State of the art

In micro- and nanohandling, the optical sensor is often the only device that can obtain position information about tools and specimen. In microhandling, optical microscopes are used to observe e.g. a manufacturing process. In contrary, a scanning electron microscope (SEM) is used for nanohandling operations, as the resolution of optical systems is not sufficient for these tasks. For both tasks, image processing is extensively used if handling processes are fully- or semi-automated. Based on the image sensor, objects are detected and classified. Additionally, the image sensor is often used as a motion tracking system for the closed-loop positioning of tools (e.g. grippers or tips); this is called visual servoing. Even if other position sensors are available for tools (e.g. internal position sensors of positioning systems), visual servoing of the end-effector is often required, e.g. to perform positioning relative to specimen. This chapter gives an overview of the state of the art. First, an overview of object-detection and motion-tracking in microrobotics is given in section 2.1. In section 2.2, an overview of FPGA-based image processing is given. FPGA-based image-processing differs from conventional image-processing; the differences are described in this section. One special object-extraction approach, the Binary Large OBject (BLOB) extraction, and its FPGA-implementations are described in section 2.3.

#### 2.1 Object tracking in microrobotics

Visual object detection and tracking are key concepts in microrobotics. Several works exist that report individual solutions to specific microrobotic problems (Papanikolopoulos et al., 1992; Pappas and Codourey, 1996; Fatikow et al., 1999, 2000; Sun and Nelson, 2002; Krupa et al., 2003; Ferreira et al., 2004; Dechev et al., 2004; Amavasai et al., 2005; Sievers and Fatikow, 2006; Hasegawa et al., 2008; Wortmann et al., 2009; Wang et al., 2009; Huang et al., 2010; Tamadazte et al., 2010, 2011; Ni et al., 2012; Tamadazte et al., 2012a; Diederichs et al., 2013).

However, all of these approaches use software-based image processing. While the throughput, and therefore the achievable update-rate, increases with each new generation of general purpose CPUs, problems like jitter, displacement and non-deterministic behavior were rarely addressed.

Ogawa et al. (2005) was one of the first to use a real-time operating system for motion tracking in microrobotics. More recent is the work of Kharboutly and Gauthier (2013). In their research, a dielectrophoresis-based system is controlled using visual servoing and a real-time operating system. The systems operated with an update-rate of 1 KHz. However, to achieve this update-rate only a small region of interest  $(256 \times 256)$  pixels is used for motion tracking. Additionally, the algorithm used is a very simple one and not robust against noise.

Hardware-based image processing has been used used inside a small sensor smart camera system for eye in hand micro-manipulation (Tamadazte et al., 2012b). Here, simple pre-processing steps can be performed inside the smart camera.

Hardware implementations for microrobotic motion tracking have only been reported by the author of this thesis (Diederichs, 2010, 2011; Diederichs and Fatikow, 2013).

There is no known previous work that addresses and analyzes the timing issues of motion tracking in microrobotics.

#### 2.2 FPGA-based image processing

Image-processing in general purpose CPUs is based on computational operations that read the input information from the memory and write the output information to the memory. The throughput of CPU-based image processing is therefore highly dependent on the memory read- and write speed. Furthermore, every image processing step needs the input to be fully available in the memory. If several image processing steps need to be performed, each processing step has to wait until the previous image processing step has finished and written the result to the memory. Each of the image processing steps therefore adds to the overall computation time for e.g. a motion tracking operation. Furthermore, CPU-based image processing has to wait until the image is fully transferred from the camera and available in the memory.

For FPGA-based image processing, several different approaches are possible. Firstly, it is possible to transfer the memory-based approach from software-based image processing to FGPAs. This may have small benefits, as it is possible to have a very high parallelism with FPGAs. However, it is also required to have a large amount of memory available. Furthermore, the read and write lanes of such a memory can become a limiting factor due to high parallelism. This kind of image processing is often referred to as *offline* image processing (Gribbon et al., 2006).

A second approach for FPGA based image processing is to use *stream-based* processing. Instead of reading and writing image data from and to the memory, the

image data is streamed line-wise, pixel after pixel, through hardware components. In stream processing, the hardware system is clocked with a fixed pixel clock. With every clock cycle, a new pixel is streamed into a hardware component. The hardware component usually has an output of one pixel value per clock cycle. For example, a thresholding system would compare the incoming pixel to a threshold and give either a black or a white pixel as output (see equation 2.1). This can easily be done in one clock cycle.

This kind of image processing has several implications that need to be taken into account when designing stream-processing algorithms. The most severe implication is that it is not possible to pause the input. In software-based image processing, it is possible to read a pixel from the memory and perform several operations before writing the result back to the memory. Using stream-based processing, with every cycle a new pixel is pushed into the hardware component.

The second implication is that random pixel access is not possible. When working on an image in the memory, all pixels of the image can be accessed. In the streaming mode, pixels that follow the current pixel are not available yet, and pixels that preceded the current one have to be stored in order to secure further access. For stream-based image processing, algorithms that require full random pixel access (e.g. working in two different areas of the image) are not feasible. However, it is possible to buffer small portions of the image to have limited access to surrounding pixels. An example is the case of line buffers, that store one or more rows of the image. With this technique local filters, also referred to as neighborhood filters, can be implemented. Examples of local filters are morphology operations or noise reduction filters such as the Gaussian filter, median filter or mean filter.

The most simple case that can be implemented with a stream processing algorithm is a point operation. The result of a point operation is only generated from the current pixel value and static inputs. Examples of point operations are thresholding, brightness changes or contrast changes. The equation for a thresholding operation that produces only black or white values is shown in equation 2.1.

$$v_o = \begin{cases} 255 & \text{if } v_i >= t \\ 0 & \text{else} \end{cases}$$

(2.1)

with  $v_i$  being the incoming pixel value, t the threshold value and  $v_o$  the outgoing pixel value.

In a software implementation, the operation would go through all image positions and write the values to a new matrix (see listing 2.1).

Listing 2.1: Pseudocode of a thresholding operation.

```

foreach y in source:

foreach x in source:

if source[x][y] >= threshold:

target[x][y] = 255;

else:

target[x][y] = 0;

end if;

end foreach;

```

In a hardware module, the operation can be written in VHDL or verilog and will be synthesized in hardware units. The VHDL code for a thresholding module is shown in listing 2.2.

The corresponding logical layout is shown in figure 2.1. While the basic concepts are the same, the implementation of the filters in an FPGA hardware system differs from the software approach. This becomes even more clear when writing local filters.

As an example, the binary morphological operation dilatation will be used (Serra, 1982). The dilatation filter, also referred to as the Minkowsky add operation, fills the whole local filter area (e.g. a  $3 \times 3$  window) to one if the value of the center is one. In a software implementation, this could be written as shown in listing 2.3 (for simplicity, border handling is not taken into account).

This implementation cannot be transferred to hardware because a hardware module cannot update several pixels in one cycle. However, the same results as the

Listing 2.2: VHDL code of a thresholding operation.

```

process(clk)

begin

if rising_edge(clk) then

if data_in >= threshold then

data_out <= (others => '1');

else:

data_out <= (others => '0');

end if;

end process;

```

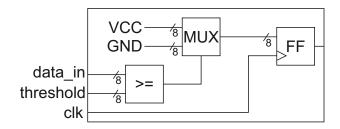

Figure 2.1: Logical layout of a hardware thresholding operation. The incoming data is compared with the threshold. If is is greater or equal, the comparator unit outputs a '1'. Otherwise, it outputs a '0'. Based on this, a mulitplexer (MUX) unit decides whether eight VCC values (i.e. binary '111111111' representing 255) or eight GND values (i.e. binary '000000000', representing 0) are outputted. The flip-flop (FF) at the end of the logic latches the output of the multiplexer at each rising clock edge.

Listing 2.3: Pseudocode of a dilatation operation.

```

target = allzero;

foreach y in source:

foreach x in source:

if source [x][y] = 1:

target[x-1][y-1] = 1;

target[x-1][y1] = 1;

target[x+1][y+1] = 1;

target[x][y-1] = 1;

target[x][y] = 1;

target[x][y+1] = 1;

target[x+1][y-1] = 1;

target[x+1][y] = 1;

target[x+1][y+1] = 1;

end if;

end foreach;

end foreach;

```

Listing 2.4: Pseudocode of a maximum operation.

```

\begin{array}{lll} & \text{for each } x \text{ in source:} \\ & \text{row1} = \max(\text{source}\,[x-1][y-1], \\ & \text{source}\,[x][y-1], \text{ source}\,[x+1][y-1]); \\ & \text{row2} = \max(\text{source}\,[x-1][y], \\ & \text{source}\,[x][y], \text{ source}\,[x+1][y]); \\ & \text{row3} = \max(\text{source}\,[x-1][y+1], \\ & \text{source}\,[x][y+1], \text{ source}\,[x+1][y+1]); \\ & \text{result}\,[x][y] = \max(\text{row1}, \text{row2}, \text{row3}); \\ & \text{end for each}; \\ & \text{end for each}; \\ \end{array}

```

dilatation can be achieved when applying a maximum filter. The maximum sets the center pixel of a window to one if one of the surrounding pixels is one. This implementation only updates one pixel, but needs to read several pixels. A software implementation for the maximum filter could be written as shown in listing 2.4.

A hardware implementation of this algorithm is possible. However, again it is not directly transferable from the software approach, as the image is not stored in the memory and pixels other than the current pixel cannot be addressed directly. Therefore, a hardware implementation has to facilitate line buffers that buffer one or more rows of the image. The line buffer then outputs one pixel of each buffer in addition to the current pixel. Using this technique, a column of several pixels can be read in one clock cycle. If a local filter with a  $3 \times 3$  window is used, two line buffers are needed. Additionally, the column that is sent by the line buffers has to be processed through a shift register to be able to calculate the output from a  $3 \times 3$  window. figure 2.2 shows the architecture of such a local filter. Such line buffers require only limited memory. For example, a line buffer for a  $3 \times 3$  window would require two lines to be buffered. For a maximum image width of 2048 and a pixel data depth of eight bit, a memory buffer would be needed that can hold 2048 elements that are 16 bit wide. FPGAs have dedicated memory blocks for this kind of buffers, referred to as BlockRam or tightly coupled memory (TCM). Furthermore, very small buffers can also be synthesized using only FPGA-slices (e.g. flip-flops). If FPGA slices are used to implement memory, this is referred to as distributed RAM.

If several image processing steps need to be performed, they need to operate one after another. In software, one step has to wait until the previous step is finished and has written its result to the memory. In FPGA-based stream-processing, operations can be pipelined. As every operation works on a pixel stream, the

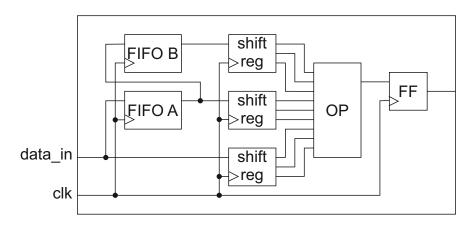

Figure 2.2: Simplified logic layout of a hardware local filter. The incoming pixel data is shifted info a FIFO (FIFO = first in first out. a small memory buffer. Elements are sent out in the same order as they ware pushed in.). The data is shifted into FIFO A as well as transferred to the shift register. The output of FIFO A is transferred into the shift register and into FIFO B. This simplified overview lacks the logic to control the FIFOs based on the columns. In theory, FIFO A contains the last line and FIFO B the line before that. When the third line is pushed into the logic, the first line is available in FIFO B and the second line in FIFO A. Thus, a three pixel column is streamed into the shift registers. The shift register shifts each incoming pixel by one, keeping the last two pixels. Together, the shift registers utilize the 3 × 3 window. The value of each shift register cell is pushed into the operation logic (OP) which can be any local filter implementation.

output stream of one operation can be used as the input stream for the next operation. Therefore, the delay of hardware-based image processing is very low. The delay introduced by each operation depends on the number of buffered elements during the operation. A point operation usually introduces a delay of one clock cycle and is in the range of 5 to 50 ns, depending on the pixel clock. For a window operation, the delay is the number of buffered lines multiplied with the image width and the clock time. For a  $3 \times 3$  window operation on an image with a width of 2048 with 100 Mhz, the introduced delay would be 41 µs.

The delay of a pipeline step in stream-processing is fixed and predictable. In offline processing and software-based image processing, the delay depends on the computation time of the image-processing algorithm. Often, the computation time is depending on the image content. For example, the first dilatation algorithm needs more steps for an image with many white pixels than for an image with only black pixels because operations are only performed based on comparisons with the image content. Stream processing performs the operation regardless of the image-content; a pixel has to be produced in every clock cycle. In most cases, the delay of stream-processing is significantly lower than the delay of offline processing. However, some cases exist where the delay of offline processing might be lower. Nevertheless, the predictability of stream-processing is always better (Bailey, 2011; Diederichs and Fatikow, 2013).

The above descriptions of stream-based image processing gave a general overview about how to of point operation and local filter implementations. To achieve correct timing for the line buffers in the local filters, control signals are used in stream processing.

#### Stream based protocol

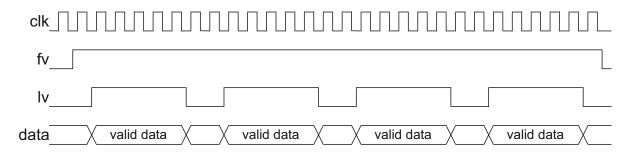

In stream-based image processing, with every clock cycle a pixel value is pushed into the logic. To be able to determine the position of the pixel value in the image, several control signals are used. These control signals follow the low-level interface of CMOS and CCD camera chips. The same control signals are also used in the CameraLink interface. In the simplest version of the protocol, one eight-bit pixel value is used. The partitioning into frames is controlled by a *frame valid* signal. The signal is high during the whole image frame. If the frame valid signal switches to low, the frame is finished. Pixels that arrive when the frame valid signal is low are not valid and must be ignored. Another signal partitions the frame into different rows. The *line valid* signal is high during the transition of one row. It changes to low on the end of each row. If the line valid signal is low, the pixel values are not valid and must be ignored. Figure 2.3 shows the interface control lines.

Figure 2.3: Control signals of stream-based image-processing. The shown protocol transmits a  $5 \times 4$  image. After the frame valid (fv) signal changes to high, the line valid (lv) signal changes to high and stays high for five clock cycles. During this time, the five pixels of the first row are transferred from left to right, one in each clock cycle. This is repeated for each of the following rows. After the frame is transferred, the frame valid signal changes to low.

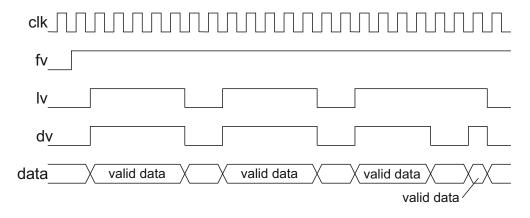

Figure 2.4: Control signals of stream-based image-processing. The general protocol remains the same. The transfer of image data can be interrupted during the transfer of a row. If this happens, the line valid (lv) signal remains high while the data valid (dv) signal changes to low. The pixel value is only valid if the line valid signal and the data valid signal are both high.

The extended interface introduces an additional data valid line. The data valid line can be used to pause the image transmission during a row. If this happens, the line valid signal remains high while the data valid signal changes to low. The pixel value is only valid if the line valid signal and the data valid signal are both high. If data valid changes to low, the number of cycles, where line valid stays high, are extended. An example of the protocol is shown in figure 2.4. This technique is useful when transferring image data with a faster clock than the image acquisition clock.

The camera link protocol extends this protocol further. In this protocol, several pixels are transferred in one clock cycle. The protocol specifies that one to eight consecutive pixels of one row can be transferred during one clock cycle. The camera link specification allows pixel clock frequencies of up to  $85\,\mathrm{MHz}$ , allowing for transfer speeds of up to  $680\,\mathrm{MP/s}$ .

While point operations and local filters are well known and have been used as hardware filters in cameras and other devices for a long time, in recent years several more complex image processing operations where transferred to FPGAs, mainly to exploit the high parallelism that is possible on FPGAs.

One of the major fields of complex image processing algorithms that benefit from faster processing times, lower latency and predictable behavior are object detection algorithms.

#### 2.3 The binary large object extraction algorithms

One object-extraction approach that is well suited for the stream-based FGPA-implementation described in section 2.2 is the binary large object (BLOB) extraction algorithm. "Technically, image objects are formed out of components that in turn are made of connected pixels. It is thus most equitable to first detect components from images. When objects have been successfully extracted from their backgrounds, they also need to be specifically identified" (Chang et al., 2004). A variety of descriptors can be used to identify objects. One possibility is to use the contour either identified by chain codes (Freeman, 1961), Fourier descriptors (Persoon and Fu, 1977), or stochastic models (He and Kundu, 1991).

To detect a component, a method called connected component labeling can be used. Using this approach, each set of connected pixels is assigned a unique label. Every pixel in the image has a label that describes its affiliation with a component. Eventually, features can be calculated based on the labels rather than based on contours.

Different approaches exist for connected component labeling. They can be classified according to the classification introduced in section 2.2.

# 2.3.1 Random-pixel access algorithms and memory-based algorithms

A variety of different algorithms based on random pixel access exist; several were transferred to an FPGA. However, these are not suited for a deterministic low latency, high speed implementation (see section 2.2).

Chang et al. (2004) used an approach based on contour boundary scans. After detecting the boundaries, all pixels inside the boundary are assigned the same label. This approach makes use of existing fast algorithms for contour detection. Hedberg et al. (2007) introduced an FPGA implementation of the algorithm.

Another approach was introduced by AbuBaker et al. (2007), using flood-filling instead of boundary scans. Here, a flood-filling is performed as soon as a raster-scan finds an unlabeled foreground pixel.

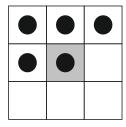

Other approaches for connected-component labeling do not need random pixel access. These approaches use a local filter to assign the label of a pixel based on the pixels in the direct neighborhood. Figure 2.5 shows the basic principle. The pixel left and the pixels above the current one are used for label assignment. If one of these pixels is already labeled (i.e. has a label ID higher than 0), the current pixel belongs to the same component and therefore is assigned the same label ID. If none of these pixels have a valid label ID, the current pixel is assigned a new label ID.

Figure 2.5: The neighborhood for connected component labeling. For the current pixel in the center, the labels of the pixels above and left are taken into consideration for the label assignment.

While the concept is fast and straightforward, several problems arise. The algorithm only knows the direct neighborhood of the current pixel. However, it is possible

that a pixel belongs to an already established component, even if the surrounding pixels belong to the background. The simplest example is a  $\cup$ -shaped object. The algorithm will encounter two vertical lines during the raster scan, and assign two different labels. Later during the raster scan, the algorithm will encounter the connection between the two regions. However, more complex objects will result in even more complex connections between assigned labels. Most implementations solve this problem by scanning the label matrix once or multiple times to correct the labels.

The different connected component labeling algorithms can be classified by the number of correction scans. An implementation that does not need additional intelligence is the multi-pass algorithm. After the first pass through the image, the label matrix is scanned backwards, correcting distinct labels to a single one. After that, the image is scanned forward again and so forth. The algorithm is finished when no correction was performed during a scan. This algorithm was implemented for an FPGA by Crookes and Benkrid (1999) and Benkrid et al. (2003). This approach needs no additional memory capacity besides the memory that stores the result label matrix. The circuit is simple and small, but the computational time depends on the complexity of the image. Additionally, the result image needs to be stored in the memory.

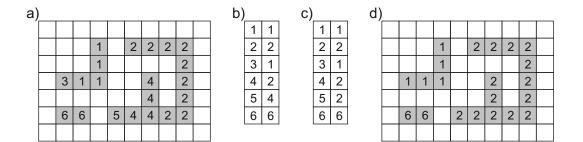

The most common approach for software implementations is the two-pass algorithm, proposed by Rosenfeld and Pfaltz (1966). This approach stores equivalent labels in an *equivalence table*. Instead of doing multiple iterations, equivalent labels are stored. After the first pass, all equivalences are resolved. A lookup table is created, which maps the initial labels to the final label. In the second pass, the lookup table is used to correct all connection labels into a single label ID. Figure 2.6 shows the process of the two-pass algorithm.

An FPGA implementation of the two-pass algorithm was introduced by Rachakonda et al. (1995). However, the two-pass algorithm requires storage of the result matrix containing the labels for each pixel. Additionally, the effort needed to transform the equivalence table to a lookup table can be complex and time consuming. The main difference between two-pass implementations is the handling of the equivalence table (Wu et al., 2005; He et al., 2007). From the two-pass algorithm, different single pass algorithms have evolved that perform an on-line handling of equivalences and performing feature detection during a single pass. These will be described in section 2.3.3.

While the approaches explained above describe the segmentation, the goal of binary large object extraction is not the exact segmentation, but the detection of robust and repeatable features (Forssén and Granlund, 2003). In all of the approaches described above, the feature detection is performed as an extra step after the

Figure 2.6: The two-pass connected component labeling algorithm. a) The labels for each foreground pixel after the first pass. During the first pass, the equivalences are stored in the equivalence table for each label. b) shows the equivalence table. From this, a lookup table (c) is generated, that contains the minimal equivalent label for each pixel. d) during the second pass, each label is replaced with its minimal equivalent label.

segmentation. The feature detection is often performed based on contours or based on the final label matrix.

#### 2.3.2 Features

Features characterize the region they were extracted from. Each feature contains significant information about the region. The features can be used to distinguish regions from each other (Bailey, 2011). They can also be used for classification (Schomaker and Bulacu, 2004). Examples of state of the art features for BLOB extraction are:

- Number of pixels: The number of pixels that belong to the found region.

- Bounding box: A rectangle that encloses the region.

- Center of gravity: the gravital center of the region, based on all x and y coordinates on the pixels inside the region.

- Contour: The contour that encloses the region.

- Convex hull: a minimal convex contour around the object.

- Perimeter: The length of the object's contour.

- Color information: The average color or grayscale.

Based on these features, found regions can be classified and grouped, e.g. for motion tracking. The features of the found regions can be compared to pre-defined data to detect whether a region belongs to the desired group and should be analyzed further.

The feature calculation can be performed based on a segmentation matrix (e.g. after connected-component labeling) or based on contours (e.g. after contour detection).

If the features need to be calculated during the segmentation instead of after the segmentation, several conditions apply. The features have to be calculated incrementally during the segmentation process. Furthermore, especially if connected component labeling is used, situations occur where previous independent segments become one segment. In this case, it must be possible to combine the calculated feature data for both segments.

Especially for hardware (i.e. FPGA) implementations of feature detection during segmentation, the incremental calculation and the combination of feature data must be achievable in one clock cycle. Feasible operations for both are sums of values or comparisons. In most cases, the operation is the same during incremental calculation and merging. The least complex feature is the number of pixels in a segmented region:

$$np = \sum_{i=1}^{n} (i)$$

(2.2)

during segmentation, the sum can be calculated step by step. During merging, two sums can simply be added. For the bounding box, the minimum and the maximum x and y values of the region's pixels are calculated:

$$x_{min} = \min(x(v_1), x(v_2), \dots, x(p_n))$$

$$x_{max} = \max(x(p_1), x(v_2), \dots, x(p_n))$$

$$y_{min} = \min(y(p_1), y(p_2), \dots, y(p_n))$$

$$y_{max} = \max(y(p_1), y(p_2), \dots, y(p_n))$$

(2.3)

During segmentation, the maximum and minimum values can also be calculated step by step, by comparing the stored value with the new value and storing the minimum or maximum, respectively:

$$x'_{max} = \begin{cases} x(p_i), & \text{if } x(p_i) > x_{max}, \\ x_{max}, & \text{otherwise} \end{cases}$$

(2.4)

The merging of two regions can be performed in a similar way.

For more complex features, computation is not directly possible. For example, the equation for the center of gravity is:

$$x_{cog} = \frac{\sum_{i=0}^{n} x(p_i)}{n}$$

$$y_{cog} = \frac{\sum_{i=0}^{n} y(p_i)}{n}$$

$$(2.5)$$

To calculate these features incrementally, the numerator and the denominator are stored and updated individually. Then, once the segmentation of a region is finished, the result is calculated once. This only has to be done once for valid objects in the image.

A second limitation for hardware implementations is that knowledge about the memory sizes is needed. While the required memory for features like number of pixels, bounding box or center of gravity is known, several features cannot be calculated without variable memory usage. The contour and the convex hull of a segment are the most prominent examples. The number of points in a contour highly depends on the object's shape and can reach from three to several thousand. However, the contour is rarely used directly for classification. Instead, the contour is used as an intermediate result to represent a segment.

In summary, several features can be derived directly during segmentation. For hardware implementations, some features are not feasible, either because they cannot be calculated incrementally, or they need variable memory.

#### 2.3.3 Single pass algorithms

The basic principle behind all single-pass approaches is to extract the data required to calculate the features during the first pass (Bailey, 1991, 2011) instead of storing the segmentation results. Different approaches exist, handling the first pass, the equivalence transformation and the feature data calculation without storing the image or intermediate results matrices.

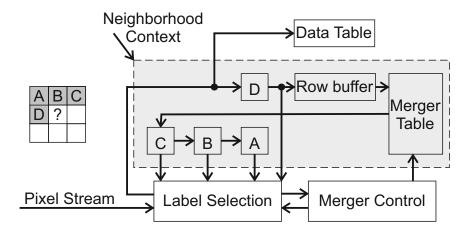

Bailey and Johnston (2007) uses the architecture shown in figure 2.7. The equivalence transformation is done on-line. The merger-control selects the label for the current pixel based on the surrounding labels similar to the first pass in the above described algorithms, but the labels from the previous line are already resolved, as far as possible, by the equivalence transformation.

The merge information is pushed onto a stack during the labeling and resolved after each line. The approach needs a line blanking time of at least 25 % of the line width to be able to resolve the stacked merge information at the end of each row. Furthermore, the approach needs 262144 label IDs for the worst case in an  $1024 \times 1024$  image. The authors propose an area-optimized algorithm that needs

Figure 2.7: The single-pass architecture used by Bailey and Johnston (2007).

less labels and therefore less RAM. However, the optimized algorithm is not robust and requires the image to be noiseless and have only few objects.

The algorithm was demonstrated by Johnston and Bailey (2008) and further optimized by Ma et al. (2008). Ma et al. (2008) introduced label reuse to further lower the resource usage of the algorithm. Additionally, the merge algorithm was extended. However, the paper states that complicated structures cannot be handled by the algorithm and must be avoided for real-time applications. Additionally, the preconditions for the line blanking time are the same as in Bailey and Johnston (2007).

The approach of Bailey and Johnston (2007) was used as a basis for the work by Klaiber et al. (2012). The paper focuses on the throughput of single-pass connected component labeling. The main idea is to divide the image into several vertical slices and compute the connected component labeling in parallel for each slice. In order to do this, the label merging needs to be communicated between the different slices. Klaiber et al. (2013) optimizes the approach in terms of resource utilization by introducing label reuse. The hardware algorithm reaches throughputs of 3.2 GB/s for images with a width of 8192 pixels. However, the approach has a very high resource utilization. Also, only one very simple feature (the bounding box) was computed by the algorithm. Furthermore, no statement for the robustness of the algorithm against noise, a large number of objects and complex structures is given.

Another approach was developed by Trein et al. (2007) (Trein et al., 2007, 2008). This approach aims for a high throughput. The main idea is to use run-length coding for adjacent foreground pixels in one line. Blocks of 32 pixels in one line are transformed into run length encoded packets (called runs). The equivalence handling differs from the approach used by Bailey and Johnston (2007): The runs are pushed into a FIFO. Then, a merging algorithm pulls the runs from the FIFO and starts the labeling and merging. With this approach, throughputs of

680 MB/s can be achieved. The algorithm already uses label re-usage. However, the implementation has several drawbacks. During tests, the authors calculated that the processing of one run takes six cycles in average. Therefore, the compression of the run-length coding must be less than 1:6. Therefore, the algorithm is not robust against noise and a large number of small objects. Furthermore, it is not possible to calculate some features, because information is lost during run length encoding, e.g. the grayscale value of each individual pixel. Additionally, other features will be complex to compute, because the information about the x position of a pixel must be extracted from the run-length coding.

Most of the reported implementations have limitations, either in the throughput, the number of extractable BLOBs or the type of features they can detect. The throughput is limited by the number of concurrent processed pixels and the maximum clock frequency of the hardware implementation. Concerning the number of extractable BLOBs, image noise as well as size and structure of objects, most algorithms have preconditions to the image content.

Therefore, a novel algorithm is proposed in this thesis that allows for robust, high speed BLOB detection and is able to calculate multiple features with low resource utilization.

# 3 A novel FPGA implementation of the BLOB extraction algorithm

As described in section 2.3, several FPGA implementations of the Binary Large OBject (BLOB) extraction algorithms have been reported. Most of these have limitations, either in the throughput, the number of extractable BLOBs or the type of features they can detect.

The throughput is limited by the number of concurrent processed pixels and the maximum clock frequency of the hardware implementation. Concerning the number of extractable BLOBs, most algorithms have preconditions for the image content.

Either they require the foreground-background ratio to be below a certain limit, or they cannot handle large numbers of small BLOBs. It is crucial that if the preconditions in a hardware-implementation are not met, the algorithm fails. In a software implementation, not meeting such preconditions would result in an increase of processing time, thus not meeting the timing requirements but still calculating correct results. The image processing is still possible, but with lower quality.

In hardware implementations, these preconditions are set on the base of the hardware-component's sizes. In particular, the size of buffers between processing elements are the main limitation and the base of those preconditions. In consequence, if the precondition is not met, a buffer overflow occurs, resulting in wrong results for the BLOB features. If the buffers are monitored for overflows, the system can detect this failure, but not correct or overcome it. Summarizing, a hardware implementation will either give wrong results or no results for the BLOB extraction if the preconditions are not met.

Besides these preconditions for the image content, most algorithms have severe preconditions for the image processing pipeline. Almost every reported algorithm relies on considerably long line blanking and frame blanking times. Line blanking is the time between the readout of two lines by the image sensor. Traditionally, these line blanking times are several tenths or hundreds of clock cycles long, due to the physical readout procedure in the camera. Frame blanking is the time between the end of one frame (i.e. image) and the start of the subsequent one. Frame blanking

times, just as line blanking times, are traditionally several tenths or hundreds of clock cycles long.

With the advancements made in camera-chips, this precondition is no longer feasible. The readout speed of modern vision sensors exceeds the transfer speed of the transfer interfaces. To obtain the maximum readout-speed, modern high-speed cameras facilitate pixel-buffers between the vision sensor and the transfer interface. As a consequence, the readout clock of the camera is set higher than the clock of the transfer interface. As a result of this, the physical line-blanking and frame-blanking times are no longer carried over to the transfer interface; the transfer interface will read the buffer content during these times. This results in line-blanking and frame-blanking times of only a single clock cycle for the BLOB algorithm.

A novel algorithm was developed aiming to overcome the identified shortcomings of the existing implementations. After defining the goals for the algorithm, a pipeline-based implementation based on the current state-of the art was developed (Diederichs, 2010, 2011). While this implementation was sufficient for simple BLOB detection tasks, it had the same limitations concerning preconditions on the image content and the line-blanking times. Experiments trying to remove those preconditions with the existing design were not successful. Consequently, a new approach without these preconditions was developed. This novel implementation is described in the following chapter.

The new algorithm has to be independent of frame-blanking and line-blanking times. It should use as few resources as possible and work with all kinds of images.

The developed approach differs from any other reported approach in several ways.

In PC-based connected component labeling, the labeling and the feature calculation is separated and performed independently. Also, the first label detection and the merging of labels is performed independently. The single-pass algorithms became possible by changing this approach. Single-pass algorithms perform the first pass and pause the first pass calculation to obtain the merging of labels. Additionally, the features are calculated on the fly and need to be merged as well. Depending on the complexity of the image, this pause can lead to a major backlog, as the image data coming from the camera is not paused. Most algorithms rely on long line-blanking times or large-background-areas to process this backlog.

The algorithm described below overcomes this paradigm by further separating the three steps: first pass, equivalence handling and feature calculation. Additionally, feature calculation is separated into different steps. The main idea is to perform feature calculation based on the regions detected by the first pass. The first pass and feature calculation is pipelined without buffers. This way, both can run at full speed with the pixel-clock, even if every pixel needs to be handled and the

line-blanking and frame-blanking times are one clock cycle, resulting in a higher throughput.

The algorithm includes a novel hardware equivalence handling. The equivalence handling is a major contribution to the robustness of the algorithm. It is performed in parallel to the first pass and feature calculation and allows for dynamic growing and shrinking of equivalence tables and the reuse of labels.

Furthermore, the novel approach performs the calculation on several pixels in one clock cycle. By doing this, the throughput and therefore the update-rate was significantly increased compared to the state of the art. First, the algorithm was developed to calculate three pixels in one clock cycle. Later, this was extended to nine pixels in one clock cycle, allowing for throughputs of up to 1.93 GB/s.

To allow for better classification, three novel BLOBs are introduced in this work. These extend the state of the art for hardware-based BLOB detection and were first reported by the author in Diederichs (2010); Diederichs et al. (2012); Diederichs and Fatikow (2013).

After describing the goals and requirements for the new algorithm, the novel implementation details of the algorithm are described. All of the following chapters are part of the original work of this thesis. First, the novel BLOB features are described. The novel equivalence handling is explained in section 3.3. In section 3.4, the hardware architecture of the novel approach is revealed. The following section explains the changes that were made to the architecture to allow for an even higher throughput, by changing the number of concurrently calculated pixels from three to nine. In section 3.6 the implementation- and test strategy is described. The chapter concludes in section 3.7.

# 3.1 Requirements and goals

The overall goal was to develop a motion tracking algorithm for microhandling tasks. Image processing is performed in order to do motion tracking for closed-loop robot control. For closed-loop control, the timing characteristics of the image processing are of great interest.

One main characteristic of a sensor is its update-rate. A higher update-rate leads to more frequent information updates for the closed-loop controller and thus to better and faster positioning. Therefore, the motion tracking algorithm should allow for high throughput.

For an FPGA-implementation this either means fast clock frequencies (i.e. above 100 Mhz) or the processing of multiple pixels in one clock cycle. It is not possible to formulate a requirement for the update-frequency, as it does not only depend on

the image-processing algorithm, but also on the camera-resolution and the camera readout-speed.

However, a requirement for the throughput can be formulated. The throughput is defined by the number of pixels that can be processed in one second (P/s). The motion tracking algorithm shall have a throughput of at least 680 MP/s. This update-rate corresponds to the update-rate of the CameraLink standard in its full configuration. With this throughput, the motion tracking algorithm can operate on a 1 MP image with an update-rate of 680 Hz.

As stated in section 1, one major issue for closed-loop controllers with image-based sensors is the update-rate deviation (update-rate jitter). Therefore, the motion tracking algorithm is required to provide a very stable update-rate. The standard deviation of the sensor signal is aimed to be below 1% of the update-rate. An update-rate of 100 Hz corresponds to an update interval of 10 ms. For an update-rate of 100 Hz, the required jitter must be below 0.1 ms.

The last timing constraint, which is derived from the requirements of the closed-loop controller, is a predictable signal latency. The latency should be as short as possible, as it describes the age of the information obtained by the sensor. However, predictability is even more important. If the closed-loop controller knows exactly about the latency, it can compensate for it. Therefore, the latency jitter should be as low as possible, but at least below 1% of the overall latency. The latency itself should be below 110% of the time needed for exposure and image transfer.

The update-rate of a camera is defined by the readout time of the sensor. While motion tracking is performed on the whole image, it cannot be faster than the readout time of the sensor.

Table 3.1 summarizes all timing requirements for the image-processing algorithm.

| Requirement        | Value | Unit                         |

|--------------------|-------|------------------------------|

| Throughput         | 680   | Mb/s                         |

| Update rate jitter | 1     | % of update-rate             |

| Latency            | 110   | % exposure and transfer time |

| Latency jitter     | 1     | % of latency                 |

Table 3.1: Requirements for the image-processing algorithm.

Furthermore, the algorithm should extend the state of the art in terms of it's classification features. For highly accurate position detection based on LEDs,

a method that is more exact than the center of gravity should be available. Furthermore, it should be possible to detect the main direction of an object that is elongated as well as the aspect ration of such objects.

# 3.2 Features

To allow for a more accurate classification, additional features are used by the algorithm. The features extend the state of the art for hardware-based BLOB detection and are part of the authors contribution.

Three new features are introduced. First, The weighted center of gravity can be used to calculate the center of an object more precisely. This feature was introduced by the author in Diederichs (2010).

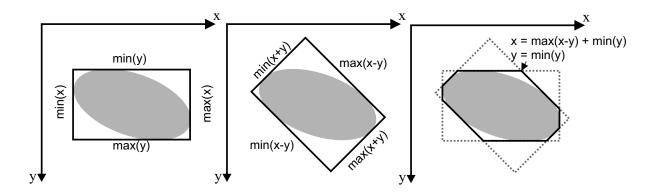

Hardware implementations cannot easily calculate an objects contour or the convex hull, because it needs a dynamic memory size for it's features (see section 2.3.2). However, it is possible to calculate several bounding rectangles, rotated by different angles. By creating the intersections of these rectangles, a rough approximation of the convex hull can be calculated.

Lastly, current features are not able to give general information about the main direction of the object or the aspect ratio. Knowing the aspect ratio and the main direction of an object is a huge benefit when objects need to be classified and the angle of the object must be tracked. The last two features were already introduced by the author in Diederichs et al. (2012); Diederichs and Fatikow (2013).

## 3.2.1 Weighted center of gravity

The weighted center of gravity is an extension of the center of gravity calculation. Instead of only using the x and y coordinates, the pixel intensity value is added as a weight (Dahmen et al., 2008).

$$x_{wcog} = \frac{\sum_{i=0}^{n} w(p_i) \cdot x(p_i)}{\sum_{i=0}^{n} w(p_i)}$$

$$y_{wcog} = \frac{\sum_{i=0}^{n} w(p_i) \cdot y(p_i)}{\sum_{i=0}^{n} w(p_i)}$$

(3.1)