Fakultät II – Informatik, Wirtschafts- und Rechtswissenschaften Department für Informatik

# Bridging the Gap between Precise RT-Level Power/Timing Estimation and Fast High-Level Simulation

A method for automatically identifying and characterising combinational macros in synchronous sequential systems at register-transfer level and subsequent executable high-level model generation with respect to non-functional properties

> Dissertation zur Erlangung des Grades eines Doktors der Ingenieurwissenschaften

> > von

Dipl.-Inform. Kai Hylla

Gutachter:

Prof. Dr. Wolfgang Nebel Prof. Dr. Wolfgang Rosenstiel

Tag der Disputation: 13. Januar 2014

### **Abstract**

Knowing a system's power dissipation and timing behaviour is mandatory for today's system development and key to an effective design space exploration. Not only does battery lifetime or design of the power supply directly depend on the power dissipation of the system. Second-order effects such as thermal behaviour or degradation effects that are directly or indirectly affected by the power dissipation must be considered, too.

Various techniques for power estimation exist at different levels of abstraction. Low-level approaches provide accurate estimation results but require a lot of computational effort. High-level approaches however, allow fast and early estimates, but lack of a deeper knowledge and understanding of the hardware, implementing the behaviour. Therefore, they can only give rough estimates. What is missing is an approach allowing fast and early estimates with respect to as many relevant hardware artefacts and physical properties as possible.

This doctoral thesis tackles the problem of a fast, yet accurate power and timing estimation of embedded hardware modules at a high-level of abstraction. A comparatively time consuming low-level estimation is performed once in order to obtain an accurate estimate. By augmenting an executable high-level simulation model with this power and timing information, fast and comprehensive simulations at a high-level of abstraction using a large set of different use cases become possible. The abstraction gap between fast simulation and accurate estimation is closed.

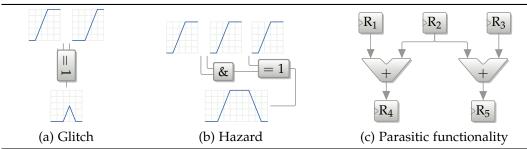

This work describes a technique for automatically identifying and characterising combinational macros in synchronous sequential systems, such as co-processors or hardware accelerators. Using a high-level synthesis, a pure behavioural high-level system description is transformed into a cycle-accurate description at structural register-transfer level. So-called hardware basic blocks, comprising a set of jointly active RT components, are identified and characterised automatically. The characterisation uses sophisticated RT-level power models, which provide accurate power and timing estimates. The characterisation also considers as many relevant physical properties and synthesis artefacts as possible. These include scheduling and binding as well as parasitic functionality, for instance. Non-functional properties such as clock or controller power as well as static power dissipation are also considered.

Using the characterised macros, a power and timing annotated high-level simulation model is generated. This C++-based virtual prototype allows a fast, yet accurate estimation of the given design with respect to various use cases and test stimuli. Beyond that, the generated prototype can be embedded into a virtual system prototype allowing a design space exploration, far more complex and comprehensive than would be feasible by using a common estimation approach at register-transfer level.

Evaluation of the presented approach is performed using a set of several industrial and academic use cases. Results show that by having an average relative error per cycle of less than  $6.93\,\%$  for most simulated clock cycles and a total error of around  $1\,\%$ , a speed-up of approximately  $160\,\times$  compared to an RT-level estimation is archived, while giving nearly cycle-accurate power estimates.

## Zusammenfassung

Das Wissen um die Verlustleistung und des zeitlichen Verhaltens eines Systems ist unerlässlich für den heutigen Systementwurf. Es ist der Schlüssel für eine effektive Exploration des Entwurfsraumes. Nicht nur die Laufzeit der Batterie oder die Auslegung der Energieversorgung hängen von der Verlustleistung ab. Nachrangige Effekte wie z. B. das thermische Verhalten des Systems oder auch Alterungseffeke, welche direkt oder indirekt von der Verlustleistung abhängen, müssen ebenfalls berücksichtigt werden.

Es existieren verschiedene Techniken für die Abschätzung der Verlustleistung sowie des zeitlichen Verhaltens auf ganz unterschiedlichen Abstraktionsebenen. Verfahren auf niedriger Ebene ermöglichen genaue Vorhersagen, benötigen jedoch einen hohen Rechenaufwand. Verfahren auf hoher Ebene hingegen erlauben schnelle und frühzeitige Abschätzungen. Ihnen mangelt es jedoch an einen tieferen Verständnis der Hardware, welche das Verhalten implementiert. Daher können sie lediglich ungenaue Vorhersagen machen. Es fehlt ein Verfahren, welches schnelle und frühe Vorhersagen unter Berücksichtigung so vieler physikalischer Eigenschaften und Hardware-Artefakten wie möglich, erlaubt.

Diese Doktorarbeit adressiert das Problem schneller aber dennoch präziser Vorhersagen der Verlustleistung und des zeitlichen Verhaltens eingebetteter Hardware-Module auf einer hohen Abstraktionsebene. Eine vergleichsweise zeitaufwändige Abschätzung auf niedriger Ebene wird einmalig durchgeführt, um eine akkurate Abschätzung zu erhalten. Durch das Anreichern eines Modells auf hoher Abstraktionsebene mit den zuvor gewonnenen Informationen, werden schnelle und umfangreiche Simulationen auf hoher Abstraktionsebene unter Verwendung von einer Vielzahl an Anwendungsfällen möglich. Die Lücke zwischen schneller Simulation und akkurater Abschätzung wird geschlossen.

Diese Arbeit beschreibt ein Verfahren für das automatisierte Erkennen und Charakterisieren von kombinatorischen Makros in synchronen sequentiellen Systemen, wie z.B. Co-Prozessoren oder Hardware-Beschleunigern. Mit Hilfe einer High-Level Synthese wird eine, zunächst rein funktionale, High-Level Systembeschreibung in eine zyklengenaue Beschreibung auf struktureller Register-Transfer Ebene erzeugt. Sogenannte Hardware Basis Blöcke, welche eine Menge gemeinsam aktiver Register-Transfer Komponenten umfassen, werden automatisch identifiziert und charakterisiert. Die Charakterisierung nutzt fortgeschrittene Power-Modelle auf Register-Transfer Ebene, welche genaue Ergebnisse bezüglich zeitlichem Verhalten sowie der Verlustleistung liefern. Die Charakterisierung berücksichtigt darüber hinaus auch so viele physikalische Eigenschaften und Synthese-Artefakte wie möglich. Dazu zählen z.B. Scheduling, Binding so wie parasitäre d.h. ungewollte Funktionalität. Nich-funktionale Eigenschaften wie Verlustleistung durch den Controller oder den Takt ebenso wie Leckströme werden ebenfalls berücksichtigt.

Mittels der charakterisierten kombinatorischen Makros wird ein High-Level Simulationsmodell erzeugt. Dieses ist um Informationen bezüglich zeitlichem Verhalten sowie der Verlustleistung angereichert. Der so erzeugte, C++-basierte virtuelle Prototyp erlaubt eine schnelle

aber dennoch genaue Abschätzung des gegebenen Systems bezüglich verschiedener Anwendungsfälle und Teststimuli. Darüberhinaus kann der erzeugte Prototyp in einen virtuellen Systemprototypen eingebettet werden. Dies erlaubt eine deutlich komplexere und umfassendere Exploration des Entwurfsraumes, als unter Verwendung einer herkömmlichen Abschätzung auf RT-Ebene möglich gewesen wäre.

Die Evaluation des hier vorgestellten Ansatzes erfolgte unter Verwendung von verschiedenen Anwendungsfällen aus akademischen und industriellem Umfeld. Die Ergebnisse zeigen, dass bei einem relativen Fehler von weniger als  $6.93\,\%$  für die meisten der simulierten Takte und einem Gesamtfehler von ca.  $1\,\%$ , eine Beschleunigung von ungefähr  $160\,\times$  im Vergleich zu einer herkömmlichen Simulation auf RT-Ebene erreicht werden kann, wobei annähernd Takt-genaue Vorhersagen bezüglich der Verlustleistung möglich sind.

We are like dwarfs standing upon the shoulders of giants, and so able to see more and see farther than the ancients.

(Bernard of Chartres, around 1120)

## Contents

| Li | st of | Figures                                                     | X        |

|----|-------|-------------------------------------------------------------|----------|

| Li | st of | Tables                                                      | XV       |

| Li | st of | Algorithms                                                  | xvi      |

| Li | st of | Listings                                                    | хiх      |

| 1  | Intr  | roduction                                                   | 1        |

|    | 1.1   | Today's Challenges in Hardware Design                       | 4        |

|    | 1.2   | Challenges and Requirements for High-Level Power Estimation | 8        |

|    | 1.3   | Scope and Contribution of this Doctoral Thesis              | 11       |

|    | 1.4   | Structure of the Thesis                                     | 12       |

| 2  | Fun   | ndamentals                                                  | 13       |

|    | 2.1   | Technical Terms                                             | 14       |

|    | 2.2   | System Design Methodologies                                 |          |

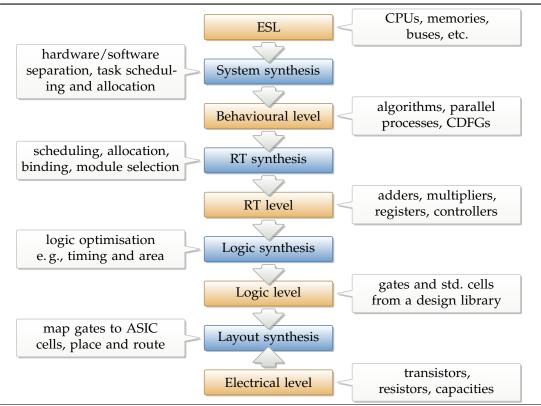

|    | 2.3   | Hardware Design and Synthesis Process                       |          |

|    | 2.4   | Power Dissipation                                           |          |

|    |       | 2.4.1 Dynamic Power                                         |          |

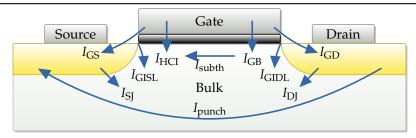

|    |       | 2.4.2 Static Power                                          |          |

|    |       | 2.4.3 Additional Sources of Power Dissipation               |          |

|    | ٥.    | 2.4.4 Power Gating                                          |          |

|    | 2.5   | Simulation Models for Power and Timing Estimation           |          |

|    |       | 2.5.1 Electrical Level                                      |          |

|    |       | 2.5.2 Logic Level                                           |          |

|    |       | 2.5.3 Register Transfer Level                               |          |

|    | 2.0   |                                                             | 28<br>29 |

|    | 2.6   | Summary                                                     | 29       |

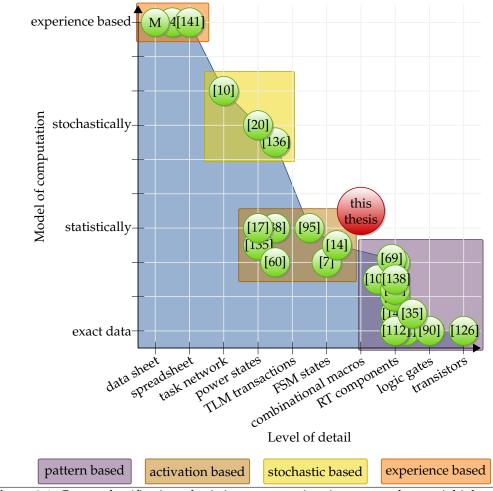

| 3  | Sta   | te of the Art                                               | 31       |

|    | 3.1   | Power Estimation                                            |          |

|    |       | 3.1.1 Pattern-Based Approaches                              |          |

|    |       | 3.1.2 Activation-Based Approaches                           |          |

|    |       | 3.1.3 Stochastic-Based Approaches                           |          |

|    |       | 3.1.4 Experience-Based Approaches                           |          |

|    |       | 3.1.5 System-Level Power Estimation                         |          |

|    |       | 3.1.6 Summary of Power Estimation Approaches                |          |

|    | 3.2   | RT-Level Abstraction Techniques                             |          |

|    | 2.2   | 3.2.1 Summary of Abstraction Techniques                     | 52<br>53 |

|    | 33    | Summary                                                     | 7        |

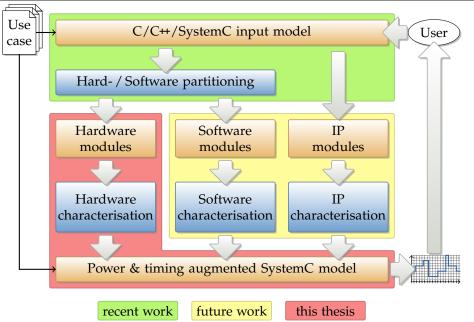

| 4 | Pow | ver Estimation & Characterisation             | <b>55</b> 58 |

|---|-----|-----------------------------------------------|--------------|

|   | 4.1 |                                               |              |

|   | 4.2 | Power Estimation Process for Digital Hardware | 60           |

|   |     | 4.2.1 Basic Idea                              | 60           |

|   |     | 4.2.2 Estimation Process Outline              | 61           |

|   |     | 4.2.3 Classification of the Proposed Process  | 65           |

|   | 4.3 | Input Model                                   | 65           |

|   |     | 4.3.1 FSM of the Controller                   | 66           |

|   |     | 4.3.2 RT Data Path                            | 66           |

|   | 4.4 | Functional Properties                         | 68           |

|   |     | 4.4.1 Preliminary Considerations              | 69           |

|   |     | 4.4.2 Hardware Basic Block Identification     | 74           |

|   |     | 4.4.3 Handling the State Explosion            | 78           |

|   |     | 4.4.4 Special Cases                           | 82           |

|   |     | 4.4.5 Hardware Basic Block Characterisation   | 84           |

|   |     | 4.4.6 Data Channels                           | 90           |

|   | 4.5 | Non-Functional Properties                     | 90           |

|   |     | 4.5.1 Controller Power                        | 91           |

|   |     | 4.5.2 Clock Power                             | 91           |

|   |     | 4.5.3 Interconnect Power                      | 92           |

|   |     | 4.5.4 Static Power                            | 92           |

|   |     | 4.5.5 Idle Power                              | 93           |

|   | 4.6 | Power Modes                                   | 94           |

|   |     | 4.6.1 Power Mode Identification               | 94           |

|   |     | 4.6.2 Power Mode Characterisation             | 95           |

|   |     | 4.6.3 Power Mode Transition Characterisation  | 96           |

|   | 4.7 | Summary                                       | 98           |

|   |     | <b>,</b>                                      |              |

| 5 | Exe | cutable Model Generation                      | 99           |

|   | 5.1 | Simulation Models                             | 101          |

|   | 5.2 | Structure of the Generated Model              | 102          |

|   | 5.3 | Model of Computation                          | 103          |

|   |     | 5.3.1 Behavioural Execution                   | 104          |

|   |     | 5.3.2 Inter-Process Communication             | 105          |

|   |     | 5.3.3 Progress of Time                        | 106          |

|   | 5.4 |                                               | 107          |

|   |     | 5.4.1 Hardware Basic Block Implementation     | 108          |

|   |     | 5.4.2 Controller Implementation               | 110          |

|   |     | *                                             | 111          |

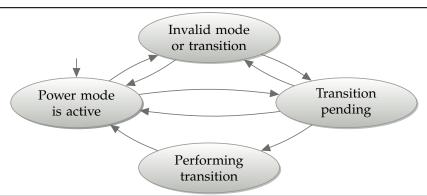

|   | 5.5 | Power Mode Model                              | 112          |

|   | 5.6 | Power and Timing Model                        | 113          |

|   |     | 5.6.1 Dynamic Power Dissipation               | 114          |

|   |     | 5.6.2 Static Power Dissipation                | 114          |

|   |     | 5.6.3 Total Power Dissipation                 | 115          |

|   |     | <b>1</b>                                      | 115          |

|   |     | •                                             | 116          |

|   | 5.7   | Virtual Prototype Interfaces                        |     |

|---|-------|-----------------------------------------------------|-----|

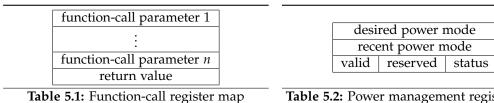

|   |       | 5.7.1 Function-Call Interface                       |     |

|   |       | 5.7.2 Power Management Interface                    |     |

|   |       | 5.7.3 TLM Wrapper                                   |     |

|   | 5.8   | Provided BAC++ Library                              |     |

|   | 5.9   | New Workflow                                        |     |

|   | 5.10  | Summary                                             | 121 |

| 6 | Eval  | uation                                              | 123 |

|   | 6.1   | Hardware Basic Block Identification                 | 125 |

|   |       | 6.1.1 Identification Process                        | 125 |

|   |       | 6.1.2 Identified Hardware Basic Blocks              | 127 |

|   | 6.2   | Design Characterisation                             |     |

|   |       | 6.2.1 Simple Characterisation                       | 132 |

|   |       | 6.2.2 Advanced Characterisation                     |     |

|   |       | 6.2.3 Non-Functional Properties                     |     |

|   |       | 6.2.4 Summary                                       | 134 |

|   | 6.3   | Power Modes                                         |     |

|   | 6.4   | Generated Model                                     |     |

|   |       | 6.4.1 Functional Correctness of the Generated Model |     |

|   |       | 6.4.2 Complexity of the Generated Model             |     |

|   |       | 6.4.3 Efficiency of the Generated Model             |     |

|   | 6.5   | Discussion of Known Problems and Issues             |     |

|   |       | 6.5.1 Micro Controlling                             |     |

|   |       | 6.5.2 Missing Information During Characterisation   |     |

|   |       | 6.5.3 Fuzzy Estimates                               |     |

|   |       | 6.5.4 Small Hardware Basic Blocks                   |     |

|   |       | 6.5.5 Multi-Cycle Operations                        |     |

|   | 6.6   | Summary                                             | 147 |

| 7 | Con   | clusion                                             | 151 |

|   | 7.1   | Outlook                                             | 154 |

|   | 7.2   | Last But Not Least                                  | 157 |

| Α | Alac  | prithms                                             | 159 |

|   | _     | Hardware Basic Block Identification                 |     |

|   |       | Basic Block Code Generation                         |     |

| В | Listi | ings                                                | 163 |

| _ | B.1   | Saturating Arithmetic (with branches)               |     |

|   | B.2   | Saturating Arithmetic (without branches)            |     |

|   | B.3   | Example Power Mode Table                            |     |

|   |       | Simulation Script Configuration                     |     |

| C | Tool  | s, Designs and Settings Used for Evaluation         | 169 |

| D | Det:  | ailed Evaluation Data                               | 177 |

| _ |       | Detailed Evaluation of Design I                     |     |

|   |       |                                                     |     |

| D.2 Detailed Evaluation of Design II           | 180 |

|------------------------------------------------|-----|

| D.3 Detailed Evaluation of Design III          | 182 |

| D.4 Detailed Evaluation of Design IV           | 184 |

| D.5 Detailed Evaluation of Design V            | 186 |

| D.6 Detailed Evaluation of Design VI           |     |

| D.7 Detailed Evaluation of Design VII          |     |

| D.8 Detailed Evaluation of Design VIII         |     |

| D.9 Detailed Evaluation of Design IX           |     |

| D.10 Detailed Evaluation of Design X           |     |

| D.11 Comparison with Logic-Level Estimation    |     |

| D.11.1 Restrictions and Required Modifications |     |

| D.11.2 Evaluation                              |     |

| D.11.3 Summary                                 | 200 |

| Symbols                                        | 201 |

| Acronyms                                       | 205 |

| Glossary                                       | 207 |

| Bibliography                                   | 215 |

| Index                                          | 227 |

| List of Own Publications                       | 231 |

## List of Figures

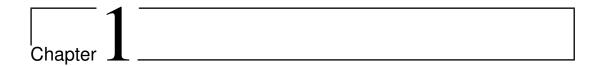

| 1.1  | Transistor gate length versus node count                      | 3  |

|------|---------------------------------------------------------------|----|

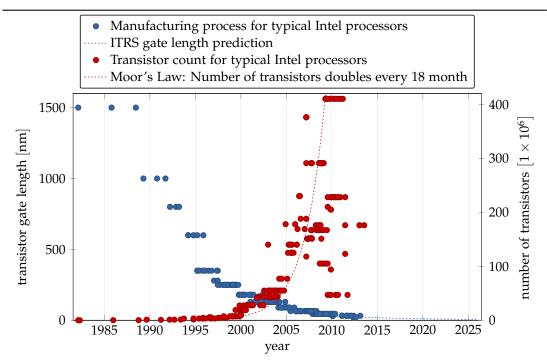

| 1.2  | Dynamic and static power dissipation                          | 5  |

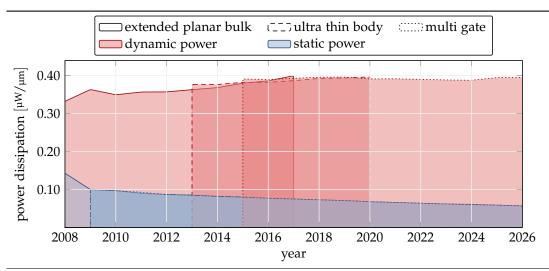

| 1.3  | ITRS gate length prediction                                   | 7  |

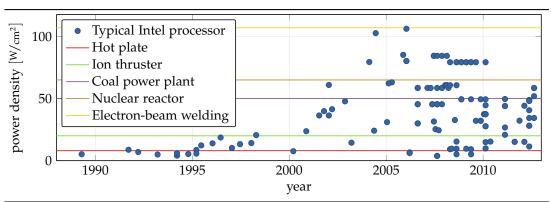

| 1.4  | Processor power density                                       | 7  |

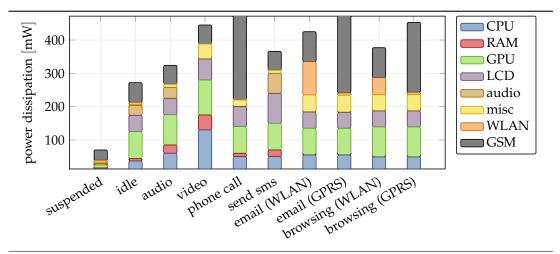

| 1.5  | Power breakdown of a smartphone                               | 9  |

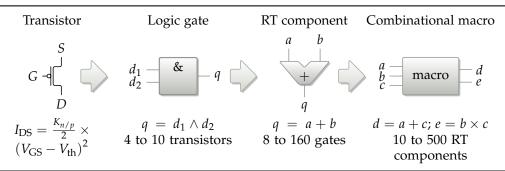

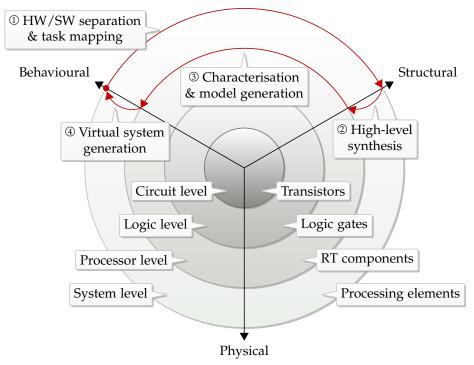

| 1.6  | Abstraction levels                                            | 10 |

| 2.1  |                                                               | 18 |

| 2.2  | 1 0                                                           | 20 |

| 2.3  |                                                               | 21 |

| 2.4  |                                                               | 22 |

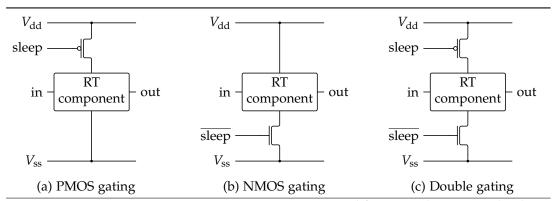

| 2.5  | Power gating                                                  | 24 |

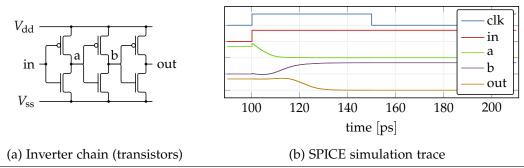

| 2.6  |                                                               | 26 |

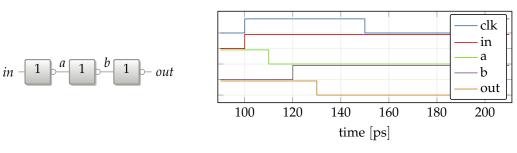

| 2.7  | Logic-level simulation of an inverter chain                   | 27 |

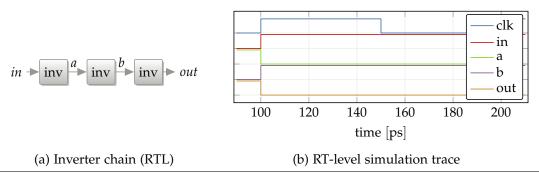

| 2.8  | RT-level simulation of an inverter chain                      | 28 |

| 3.1  | Coarse classification of existing power estimation approaches | 48 |

| 4.1  | Design process, as proposed by the project COMPLEX            | 59 |

| 4.2  |                                                               | 61 |

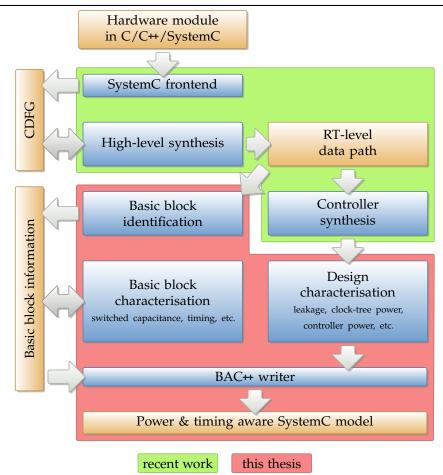

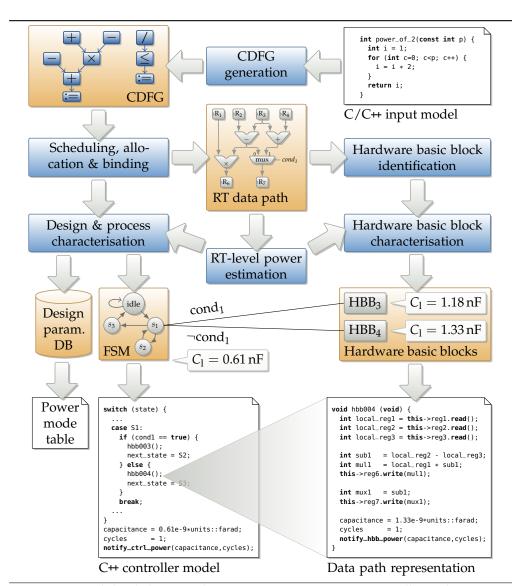

| 4.3  | Synthesis-based characterisation process                      | 63 |

| 4.4  |                                                               | 64 |

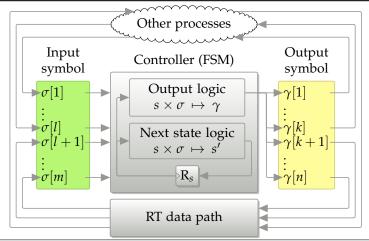

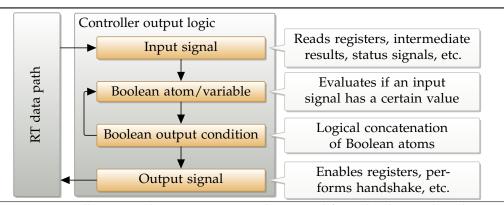

| 4.5  | Controller interaction                                        | 67 |

| 4.6  |                                                               | 69 |

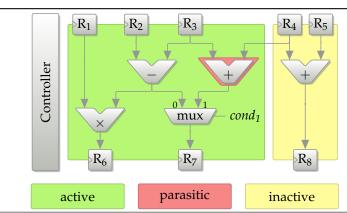

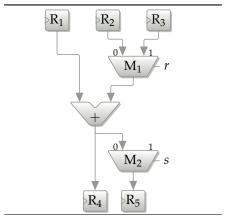

| 4.7  |                                                               | 75 |

| 4.8  | Required assignment identification                            | 80 |

| 4.9  | Assignment hardware basic block                               | 83 |

| 4.10 |                                                               | 83 |

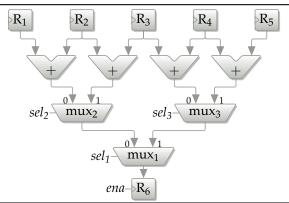

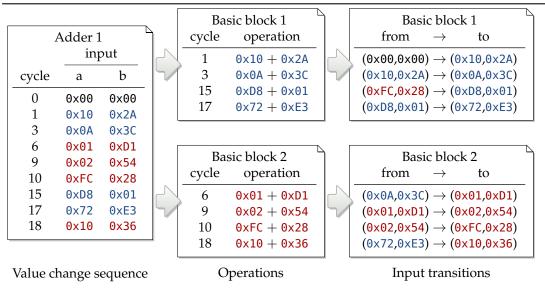

| 4.11 | Obtaining times an RT component is active                     | 86 |

| 4.12 | Unbinding of operations                                       | 88 |

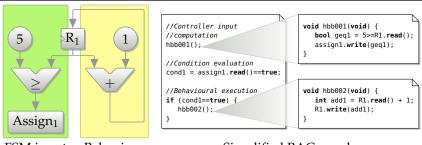

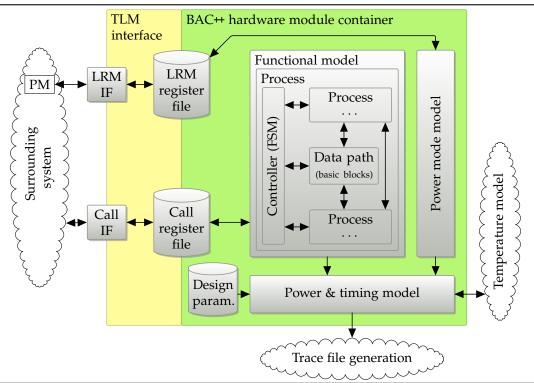

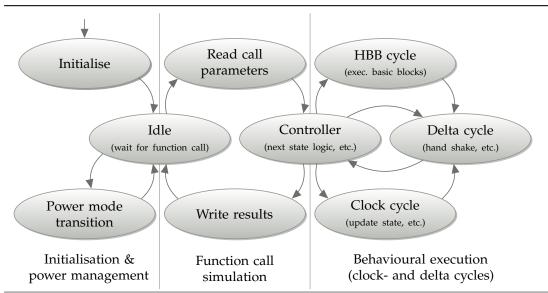

| 5.1  | Structure of a generated BAC++ module                         | 02 |

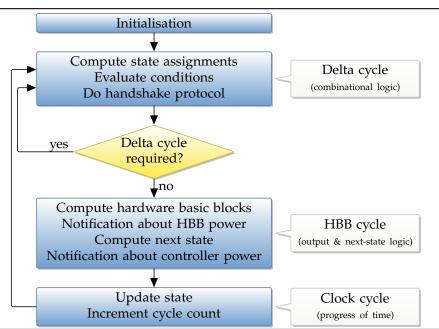

| 5.2  | Main simulation loop                                          |    |

| 5.3  | Behavioural execution                                         |    |

| 5.4  |                                                               | 13 |

| 5.5  |                                                               | 21 |

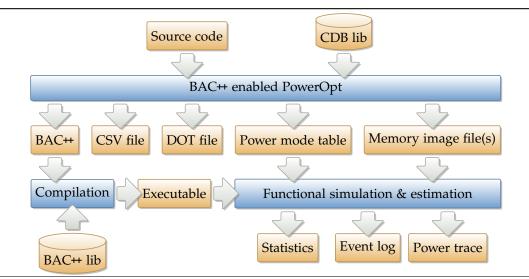

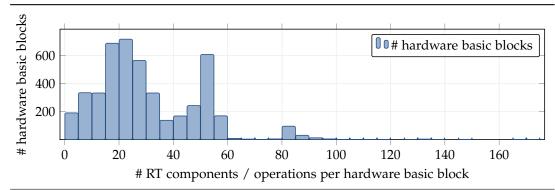

| 6.1  | Histogram of RT components per hardware basic block           | 28 |

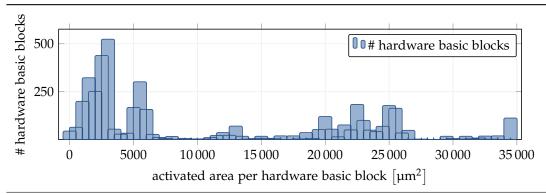

| 6.2  | Histogram of active area per hardware basic block             |    |

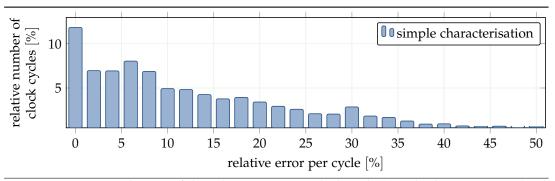

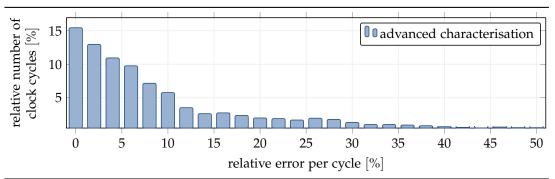

| 6.3  | •                                                             | 32 |

| 6.4  |                                                               | 33 |

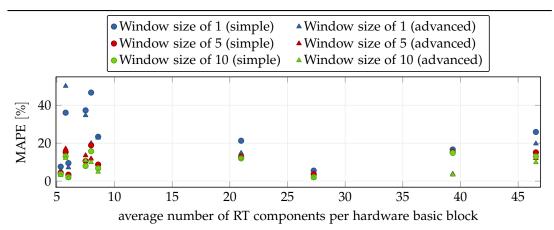

| 6.5  | Average error per sample vs. average basic block size              | . 135 |

|------|--------------------------------------------------------------------|-------|

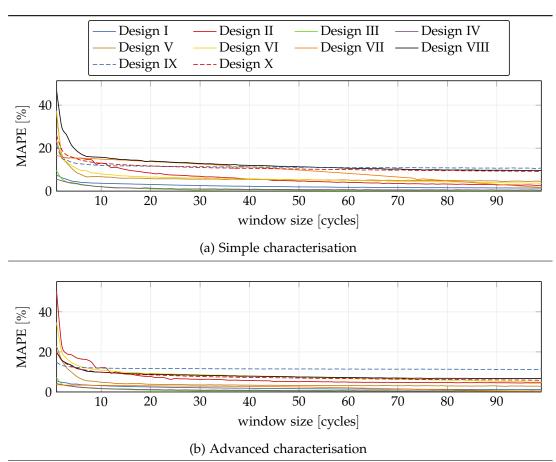

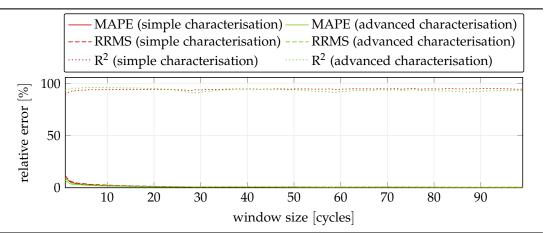

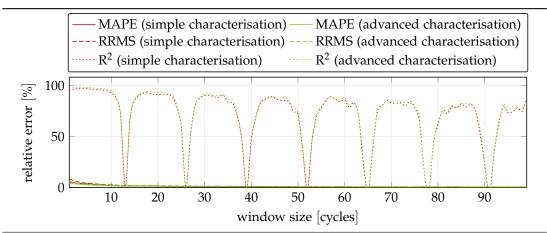

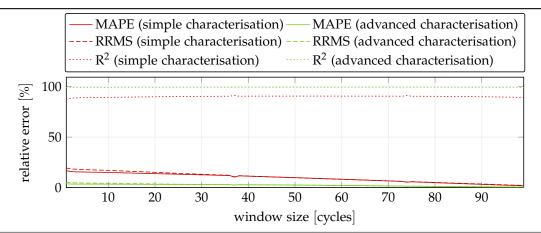

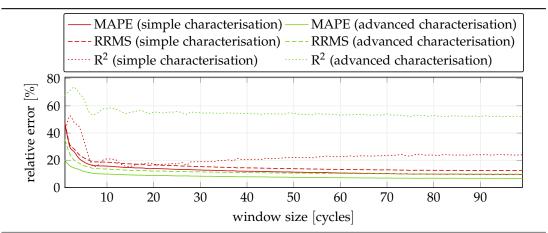

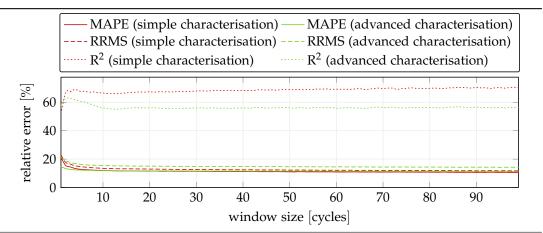

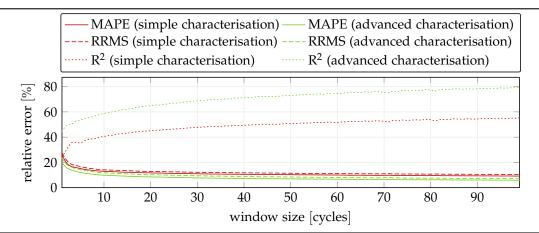

| 6.6  | Relation between average error per sample and sampling window size |       |

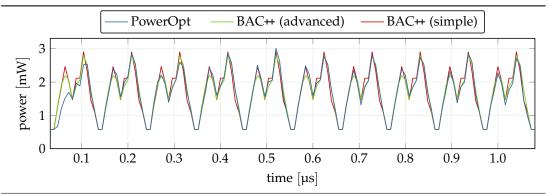

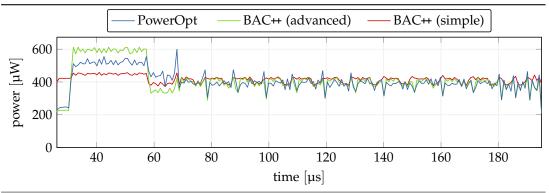

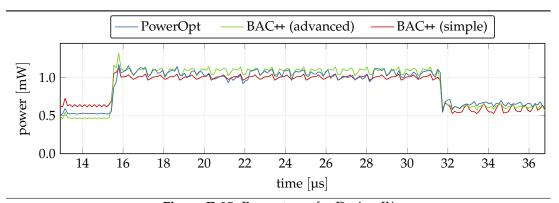

| 6.7  | Power trace with respect to different power modes                  |       |

| 6.8  | Average number of RT components vs. speed-up                       |       |

| 6.9  | Operation saturation with branches                                 |       |

|      | Register power trace                                               |       |

|      | Dynamic power dissipation with respect to multi-cycle operations   |       |

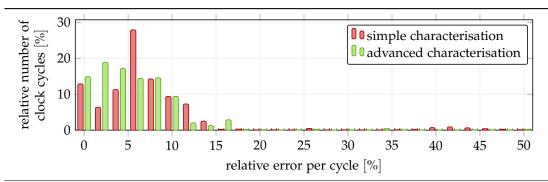

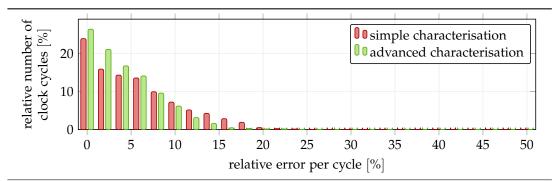

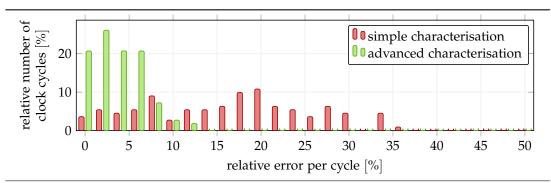

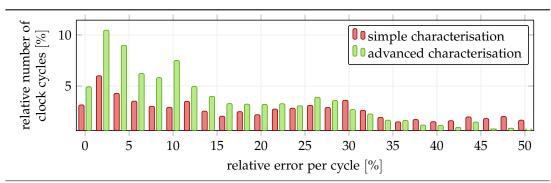

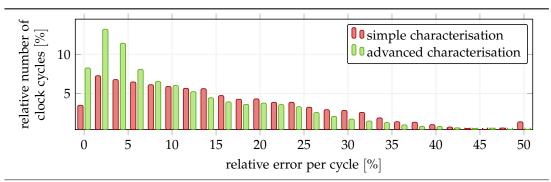

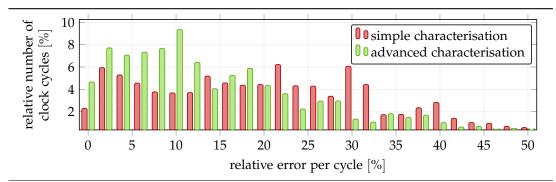

|      | Histogram of the relative error per clock cycle                    |       |

| 71   | Control amountarity of decision manufacture                        | 150   |

| 7.1  | Spatial granularity of design properties                           | . 133 |

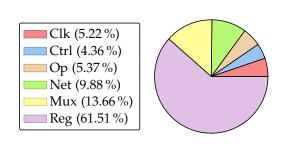

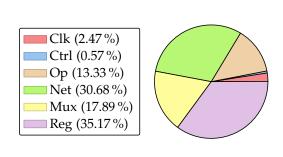

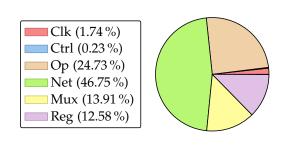

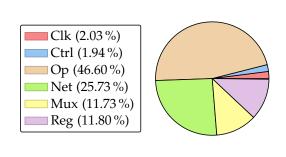

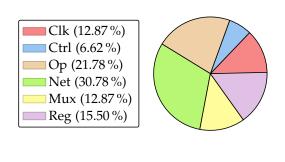

| C.1  | Design I energy breakdown                                          |       |

| C.2  | Design II energy breakdown                                         |       |

| C.3  | Design III energy breakdown                                        | . 172 |

| C.4  | Design IV energy breakdown                                         | . 172 |

| C.5  | Design V energy breakdown                                          | . 173 |

| C.6  | Design VI energy breakdown                                         | . 173 |

| C.7  | Design VII energy breakdown                                        | . 174 |

| C.8  | Design VIII energy breakdown                                       | . 174 |

| C.9  | Design IX energy breakdown                                         | . 175 |

| C.10 | Design X energy breakdown                                          | . 176 |

| C.11 | Design XI energy breakdown                                         | . 176 |

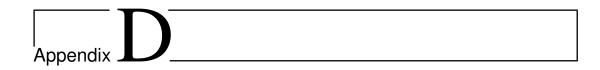

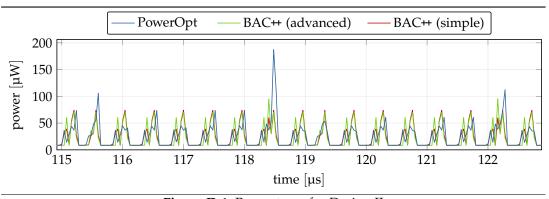

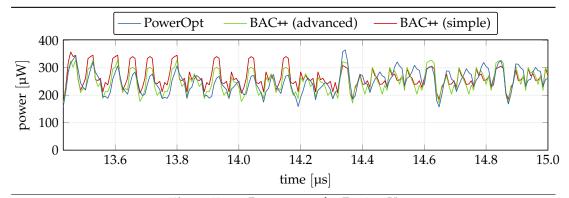

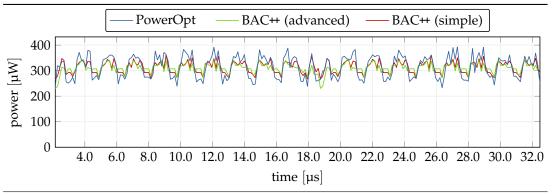

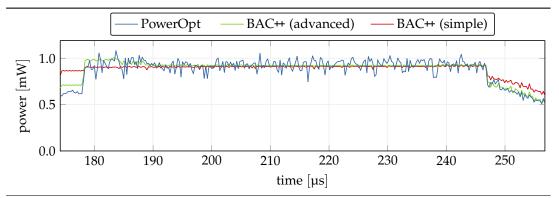

| D 1  | Power trace for Design I                                           | 178   |

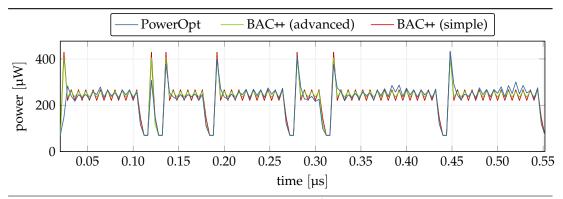

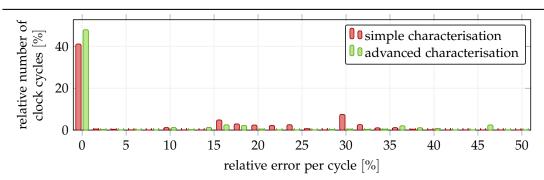

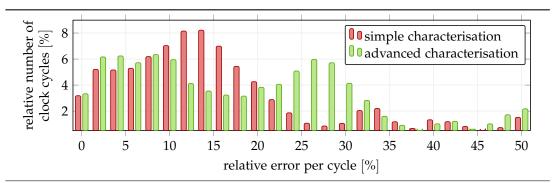

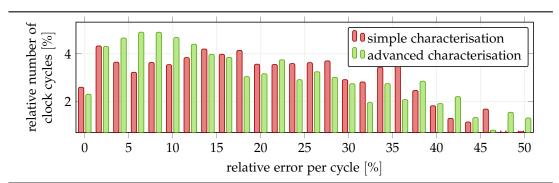

|      | Distribution of the relative error per cycle for Design I          |       |

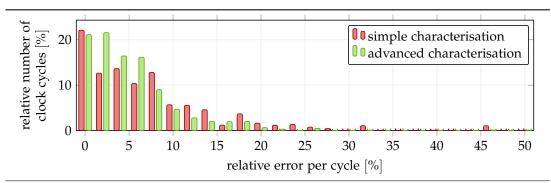

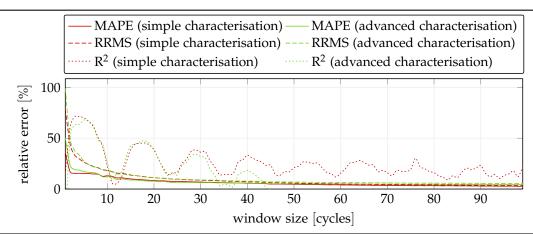

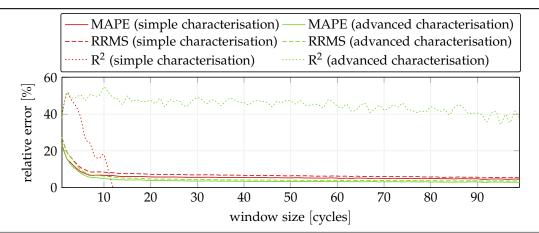

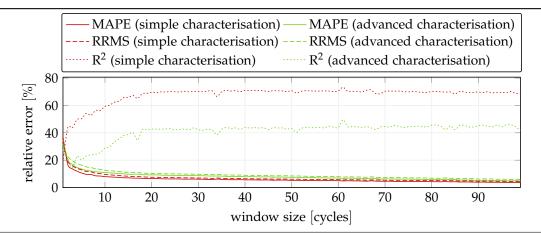

|      | Average relative error vs. sampling window size for Design I       |       |

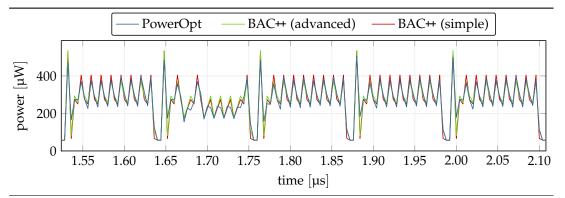

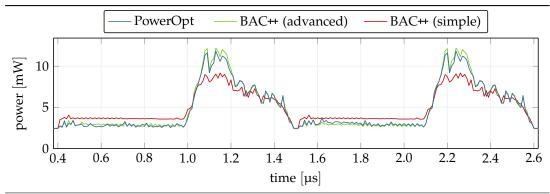

|      | Power trace for Design II                                          |       |

|      | Distribution of the relative error per cycle for Design III        |       |

|      | Average relative error vs. sampling window size for Design II      |       |

|      | Power trace for Design III                                         |       |

|      | Distribution of the relative error per cycle for Design III        |       |

|      | Average relative error vs. sampling window size for Design III     |       |

|      | Power trace for Design IV                                          |       |

|      | Distribution of the relative error per cycle for Design IV         |       |

|      | Average relative error vs. sampling window size for Design IV      |       |

|      | Power trace for Design V                                           |       |

|      | Distribution of the relative error per cycle for Design V          |       |

|      | Average relative error vs. sampling window size for Design V       |       |

|      | Power trace for Design VI                                          |       |

|      | Distribution of the relative error per cycle for Design VI         |       |

|      |                                                                    |       |

|      | Average relative error vs. sampling window size for Design VII     |       |

|      | Power trace for Design VII                                         |       |

|      | Distribution of the relative error per cycle for Design VII        |       |

|      | Average relative error vs. sampling window size for Design VII     |       |

|      | Power trace for Design VIII                                        |       |

|      | Distribution of the relative error per cycle for Design VIII       |       |

| D.24 | Average relative error vs. sampling window size for Design VIII    | . 193 |

| D.25 Power trace for Design IX                                     | 194 |

|--------------------------------------------------------------------|-----|

| D.26 Distribution of the relative error per cycle for Design IX    |     |

| D.27 Average relative error vs. sampling window size for Design IX | 195 |

| D.28 Power trace for Design X                                      | 196 |

| D.29 Distribution of the relative error per cycle for Design X     | 197 |

| D.30 Average relative error vs. sampling window size for Design X  | 197 |

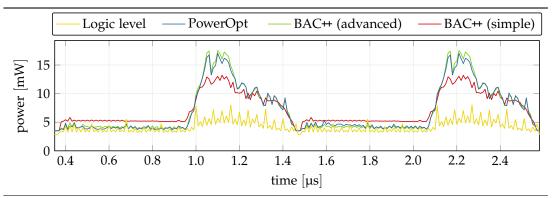

| D.31 Logic-level power trace                                       | 199 |

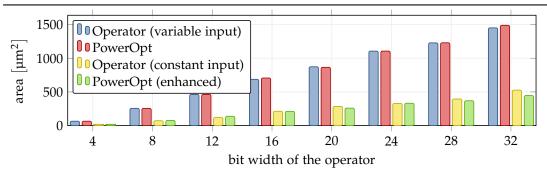

| D.32 Area reduction for operators with constant input              | 200 |

## List of Tables

| Required assignments                                                            | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function-call register map                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| · · · · · · · · · · · · · · · · · · ·                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                 | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Computational enort                                                             | 147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Used Tools                                                                      | 169                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Design I characteristics                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Design II characteristics                                                       | 171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Design III characteristics                                                      | 172                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Design IV characteristics                                                       | 172                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Design V characteristics                                                        | 173                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Design VI characteristics                                                       | 173                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Design VII characteristics                                                      | 174                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Design VIII characteristics                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Design IX characteristics                                                       | 175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

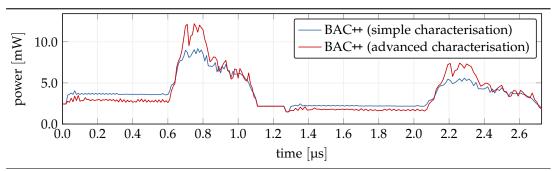

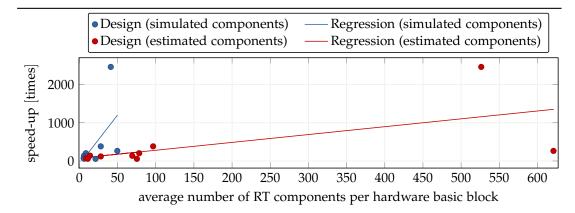

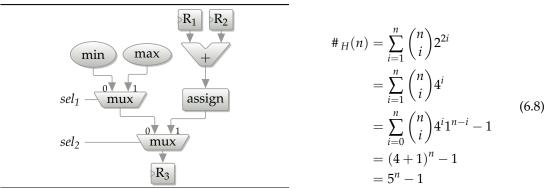

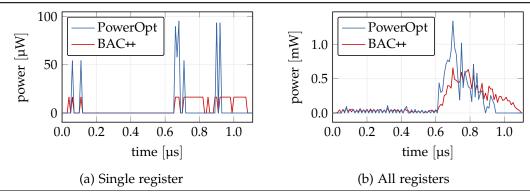

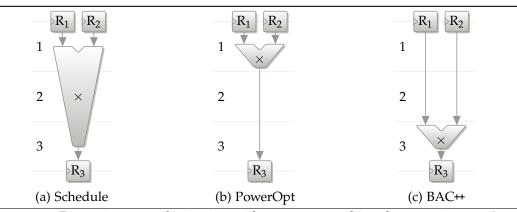

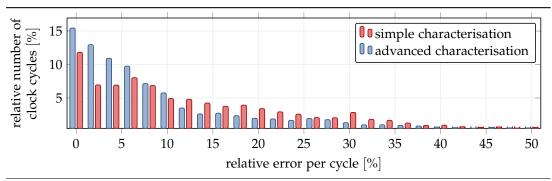

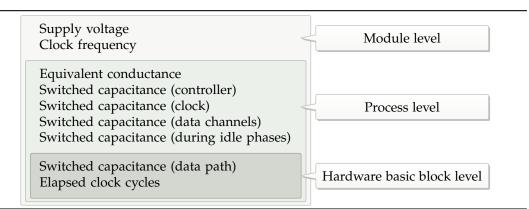

| Design X characteristics                                                        | 176                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |